| APPLI     | CATION |          |         | R   | EVISIONS    |     |

|-----------|--------|----------|---------|-----|-------------|-----|

| NEXT ASSY | USEDON | APPROVED | DATE    |     | DESCRIPTION | REV |

| - A-E A-1 |        |          |         | PCN | 31767       | A   |

| <b>-</b>  |        | a Howe   | 1-17-84 |     | 31949       | B   |

| -         |        |          |         |     | 32034       | C   |

| •         |        |          |         |     | 32289       | D   |

TECHNICAL MANUAL

NS23C

256KB MEMORY

| •  | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                        |     |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|-----|

|    | BY y. Pipenli// DATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TITLE | NS23C Technical Manual |     |

|    | CHK Spel 1) Three?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ]     |                        |     |

| •  | APPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                        |     |

|    | APPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                        | REV |

| 77 | National Semiconductor Corporation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A     | 420 <b>0</b> 10105-001 | 77  |

|    | The second secon |       |                        |     |

## TABLE OF CONTENTS

| CHAP1 | TER I GENERAL DESCRIPTION            | PAGE        |

|-------|--------------------------------------|-------------|

| 1.1   | Introduction                         | 5           |

| 1.2   | Memory Capacity                      | 5           |

| 1.3   | Modes of Operation                   | 6           |

| 1.4   | Timing                               | 6           |

| 1.5   | Power Requirements                   | 7           |

| 1.6   | Mechanical Description               | 7           |

| 17    | Dimensions                           | 7           |

| 1.8   | Environmental Specifications         | 8           |

| 1.9   | Reliability and Maintainability      | 8           |

| CHAP  | TER II THEORY AND OPERATION .        |             |

| 2.0   | General                              | 9           |

| 2.1   | Interface Specifications             | 9           |

| 2.2   | Interface Signals                    | 9           |

|       | 2.2.1 Control Signal Description     | <b>10</b> . |

|       | 2.2.2 Output Signal Description      | 11          |

|       | 2.2.3 Extended Address Lines         | 12          |

|       | 2.2.4 Bidirectional Signals          | 13          |

| 2.3   | I/O Connector Pin List               | 13          |

| 2.4   | Timing                               | 15          |

| 2.5   | Memory Card Options                  | 23          |

|       | 2.5.1 Parity Generation and Checking | 23          |

|       | 2.5.2 Extended Address Space         | 23          |

|       | 2.5.3 Reserved I/O Space             | 24          |

|       | 2.5.4 Block Mode Transfers           | 24          |

|       | 2.5.5 Battery Backup                 | 24          |

| 2.6   | Control and Status Register          | 24          |

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

SCALE

SHEET

2 **OF**

| CHAPTE | R III INSTALLATION                    | PAGE        |  |

|--------|---------------------------------------|-------------|--|

| · 7 O  | General                               | 27          |  |

| 3.0    | Tools Required                        | 27          |  |

| 3.1    | Unpacking and Inspection              | 27          |  |

| 3.2    | System Verification                   | 27          |  |

| 3.3    | Starting Address Selection            | 27          |  |

| 3.4    | Memory Size Selection                 | · <b>28</b> |  |

| 3.5    | CSR Address Selection                 | 28          |  |

| 3.6    |                                       | 28          |  |

| 3.7    | I/O Page Size Selection               | 28          |  |

| 3.8    | Parity Detection                      | 29          |  |

| 3.9    | Internal/External Refresh             | 29          |  |

| 3.10   | Battery Backup                        | 29          |  |

|        | Block Mode Installing the NS23C       | 36          |  |

| CHAPT  | ER IV DIAGNOSTICS AND TROUBLESHOOTING |             |  |

| 4.1    | General                               | 37          |  |

| 4.2    | ZKMA                                  | 37          |  |

| 4.3    | Running ZKMA                          | 38          |  |

| 4.4    | ZQMC                                  | 39          |  |

| 4.5    | Running ZQMC                          | 40          |  |

| 4.6    | ZMSD                                  | 41          |  |

| 4.7    | Running ZMSD                          | 42          |  |

| 4.8    | VMSA                                  | 44          |  |

| 4.9    | Running VMSA                          | 45          |  |

| 4.10   | 11/23 Plus System Diagnostics         | 49          |  |

| CHAP   | TER V MAINTENANCE                     |             |  |

| 5.0    | General                               | 52          |  |

| 5.1    | Troubleshooting                       | 52          |  |

420010105-001

D

52

SCALE

SHEET 3 OF

## TABLES AND FIGURES

| TABLE      |                                                                                | PAGE       |   |

|------------|--------------------------------------------------------------------------------|------------|---|

| 1-1        | Access and Cycle Timing                                                        | 6          |   |

| 1-2        | Power Requirements                                                             | 7          |   |

| 1-3        | Dimensions                                                                     | 7          |   |

|            |                                                                                |            |   |

| 2-1        | Input Control Signals                                                          | 9          |   |

| 2-2        | Output Control Signals                                                         | 11         |   |

| 2-3        | Extended Address Signals                                                       | 12         |   |

| 2-4        | Bidirectional Signals                                                          | 13         |   |

| 2-5        | I/O Connector Pin List                                                         | 14         |   |

| 3-1        | Starting Address Selection                                                     | 31         |   |

| 3-1        | Address Range Selection                                                        | 32         |   |

| 3-2        | CSR Address Selection                                                          | 32         |   |

| 3-4        | Memory Size                                                                    | 33         |   |

| 3-5        | Extended Address Selection                                                     | 33         |   |

| 3-6        | Jumper Definitions                                                             | 34         |   |

|            |                                                                                |            |   |

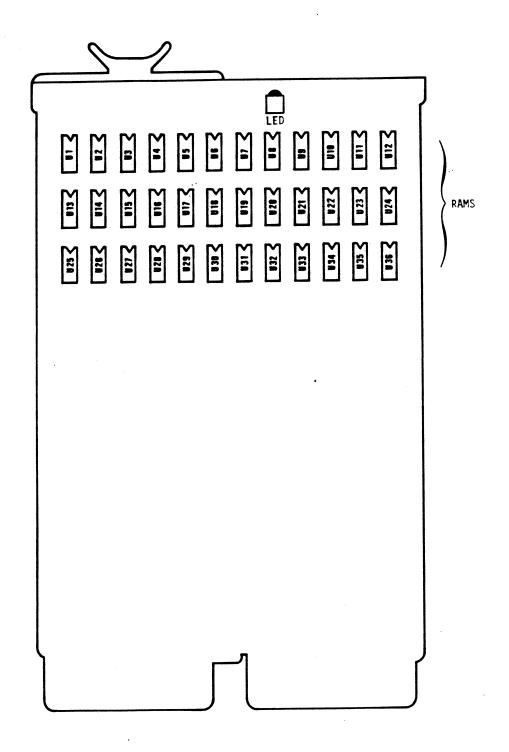

| 4-1        | NS23C Bit Locator Chart                                                        | <b>4</b> 8 |   |

| 4-2        | 11/23 Plus Diagnostic/Bootstrap                                                | 49         |   |

| FIGURE     |                                                                                | PAGE       |   |

|            |                                                                                | 16         |   |

| 2-1<br>2-2 | DATI Bus Cycle Timing (Read)  DATO, DATOB Bus Cycle Timing (Write, Write/Byte) | 17         |   |

| 2-2        | DATIO and DATIOB Bus Cycle Timing (Read-Modify-Write)                          | 18         |   |

| 2-3        | DATBI Bus Cycle Timing (Read Block)                                            | 19         |   |

| 2-5        | DATBO Bus Cycle Timing (Write Block)                                           | 20         |   |

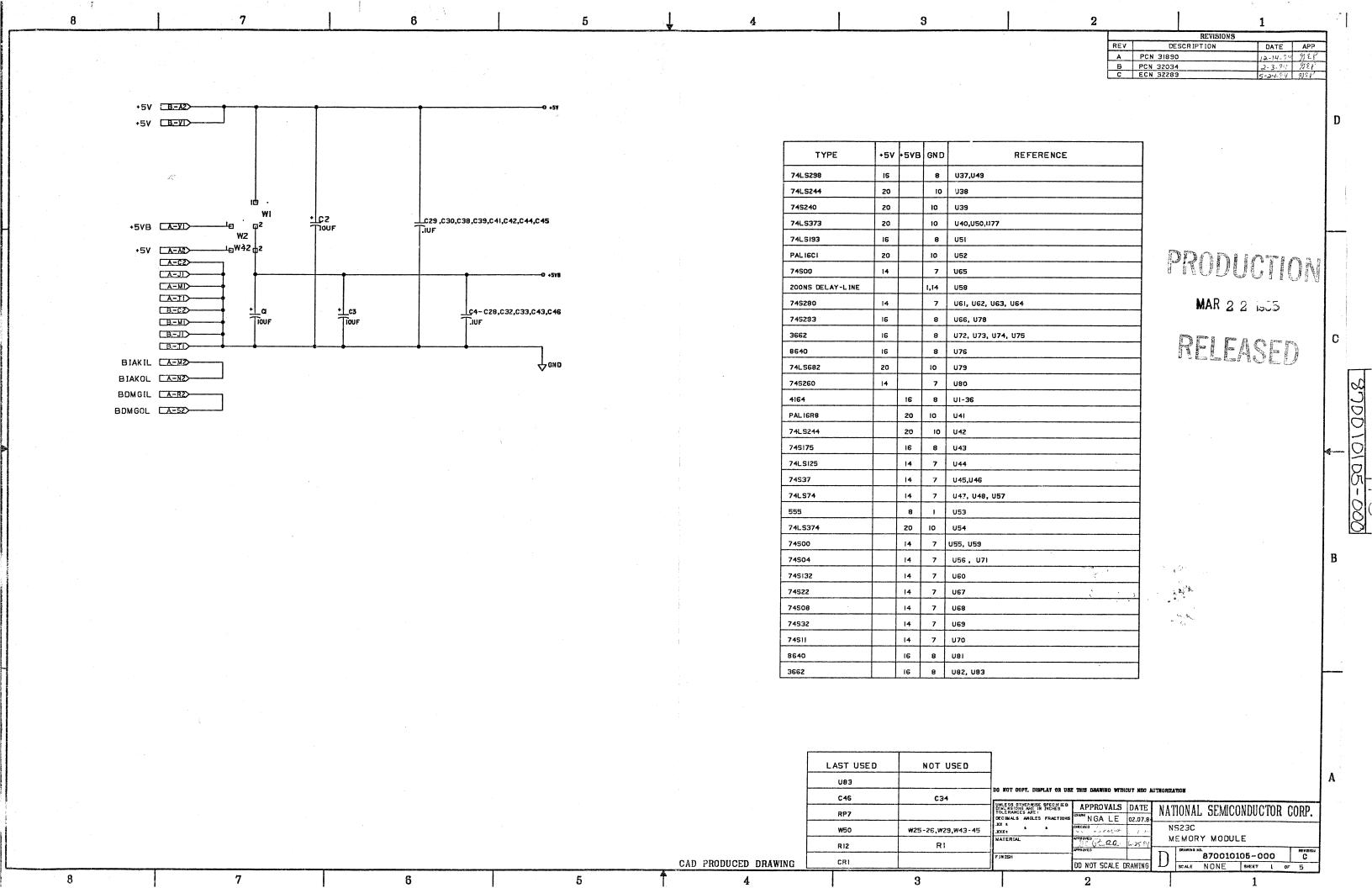

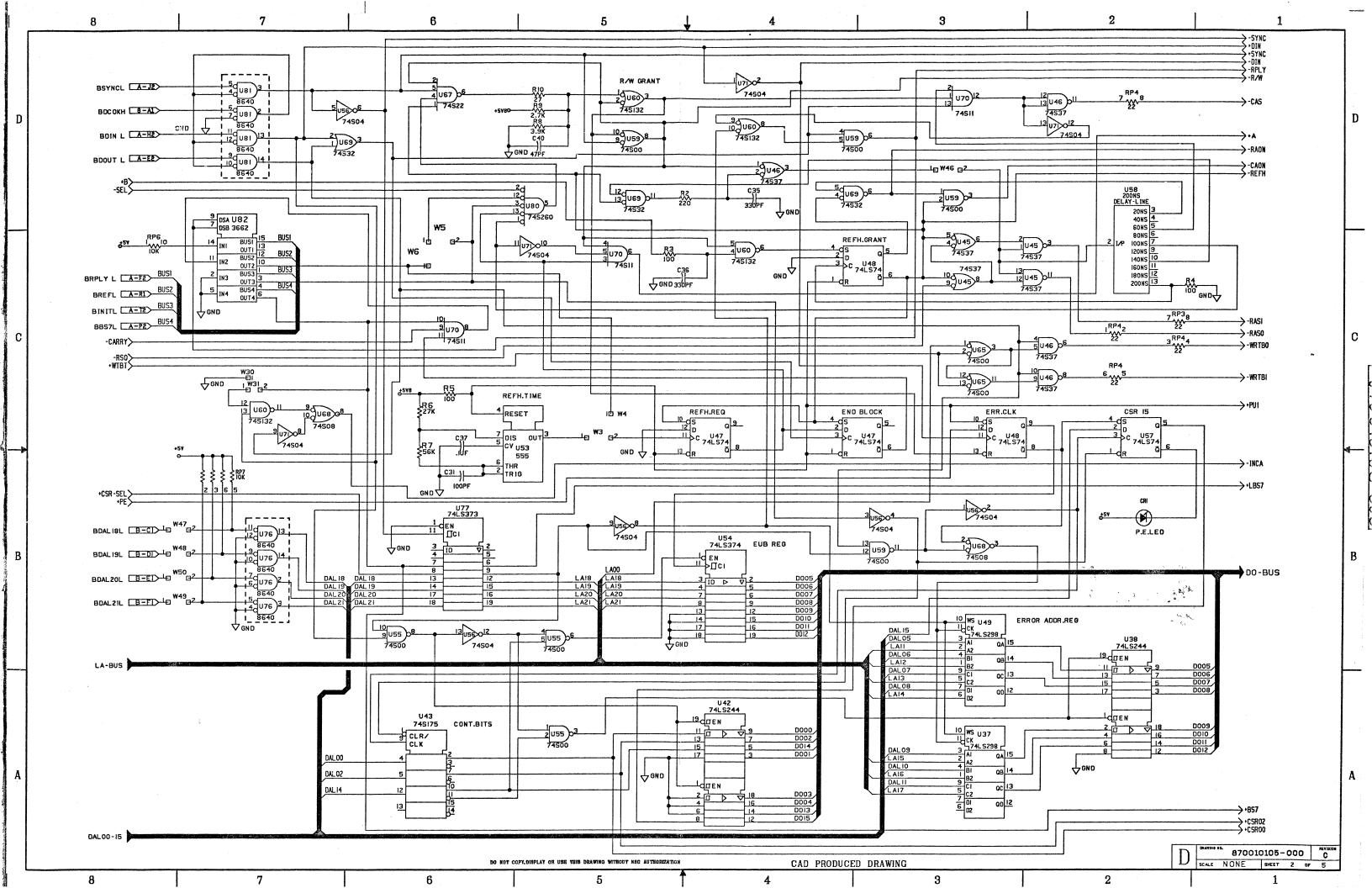

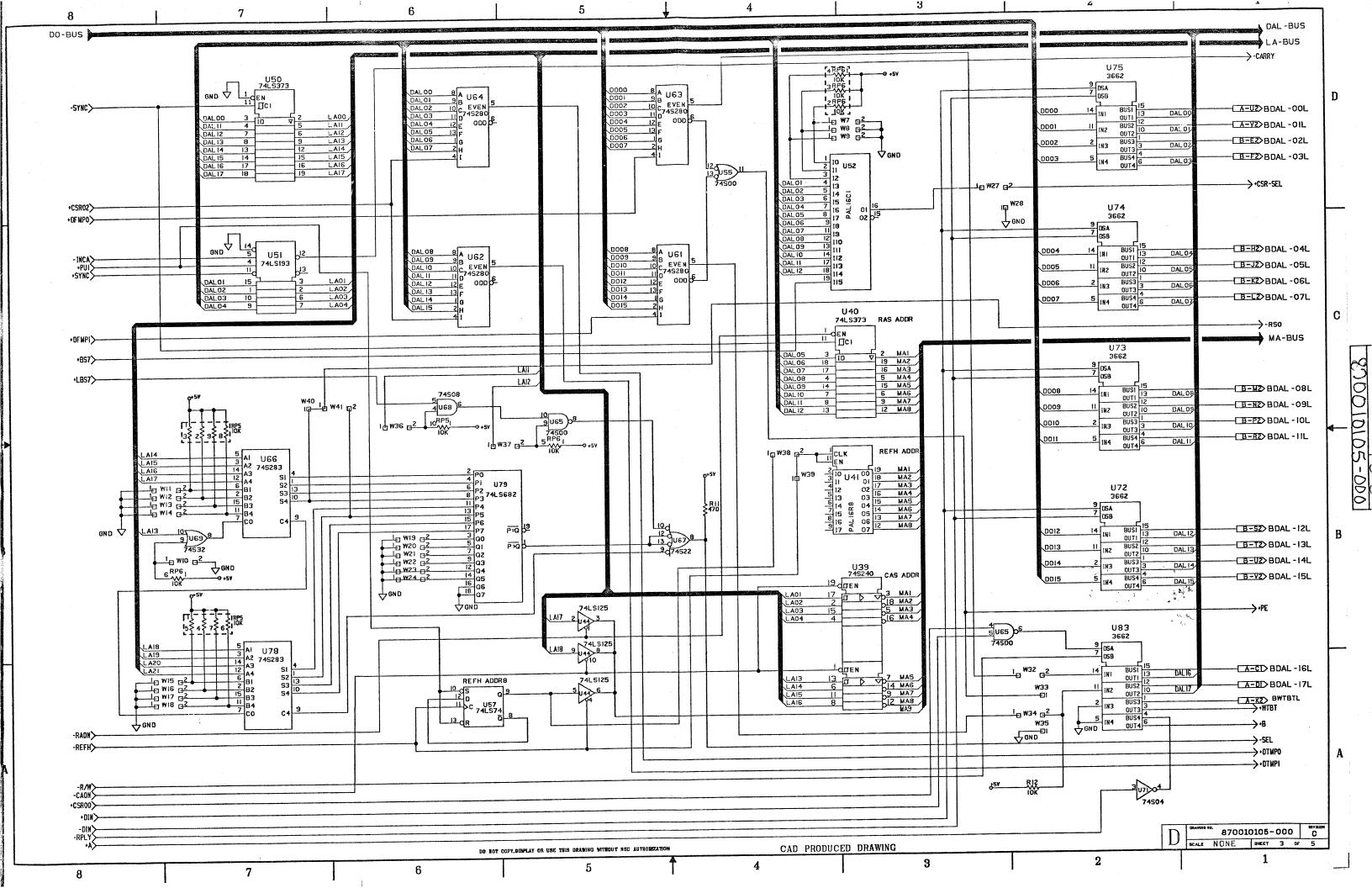

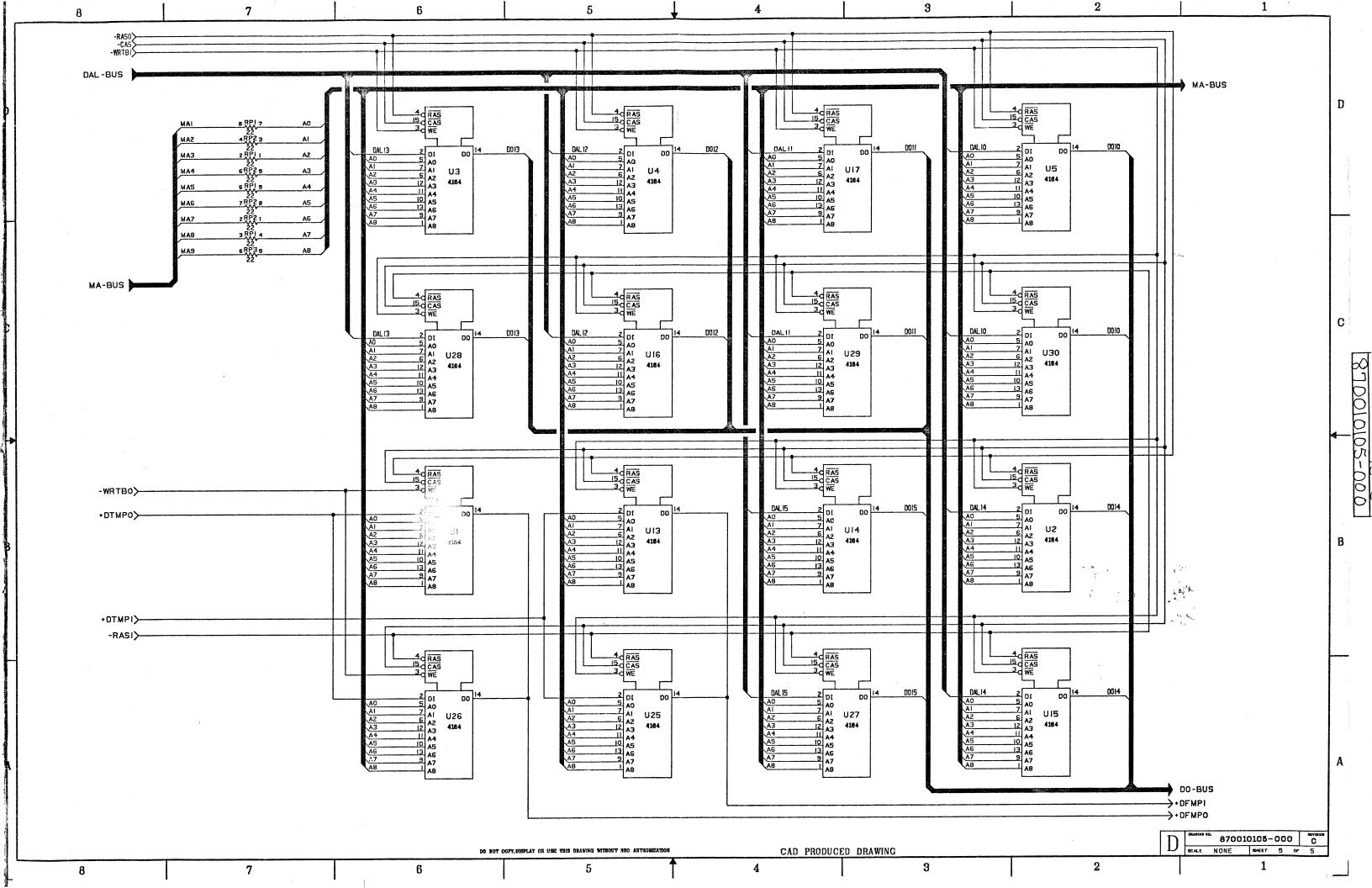

| 2-6        | Block Diagram                                                                  | 21         |   |

| 2-7        | External Refresh Timing                                                        | 22         |   |

| 2-8        | CSR Bit Assignment                                                             | 24         |   |

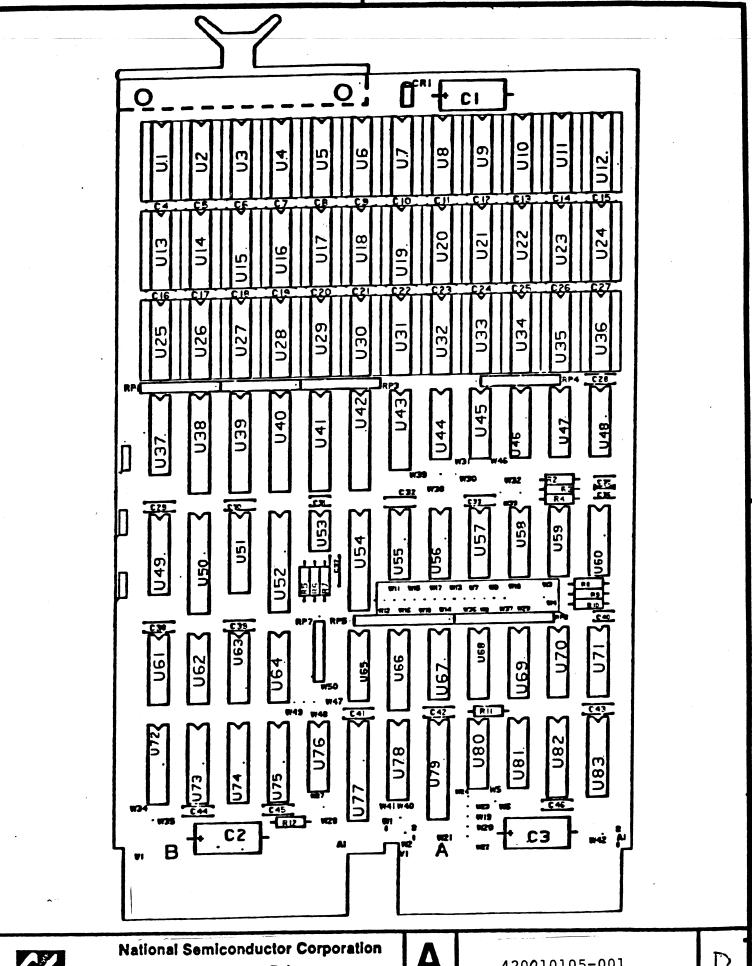

| 3-1        | NS23C Assembly Drawing                                                         | 30         |   |

| 4-1        | NS23C RAM Locations                                                            | 47         |   |

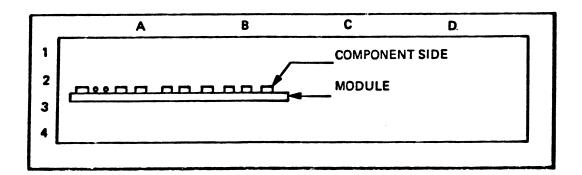

| 5-1        | Module Orientation                                                             | 52         |   |

|            | National Semiconductor Corporation                                             |            | T |

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 4

**OF** 52

#### CHAPTER I GENERAL DESCRIPTION

#### 1. 1 INTRODUCTION

The NS23C Memory Card is an add-in memory for Digital Equipment Corporation (DEC)\* LSI Microcomputer Systems.

The card has been designed to be mechanically and electrically compatible with the LSI-11, LSI-11/2, MICRO/PDP-11, MICRO/VAX, LSI-11/23, and LSI-11/73 systems. The NS23C is compatible with DEC MSV11-L series semiconductor memory modules, and can be installed in the H9270, H9281, H9273-A, DDV11-B or the H9275 and H9276 backplanes.

On board features include battery back up, 18 to 22 bit address decode, control and status register (CSR) for parity error control and block mode transfers.

#### 1.2 MEMORY CAPACITY

The standard memory capacity of the NS23C is 131,072 words by 18 bits (128KW x 18 bits) with optional capacities available from a minimum of 65,536 words by 18 bits (64KW x 18 bits) to a maximum of 131,072 words by 18 bits (128KW x 18 bits).

The starting address of the NS23C can be assigned anywhere within the LSI-11 128KW address space (in 4KW increments), or within the LSI-11 2MW address space (in 4KW increments) if extended addressing is implemented.

\* DEC, MICRO/PDP-11, MICRO/VAX, LSI-11, and PDP are trademarks of Digital Equipment Corporation.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

**]**

SCALE

SHEET 5 OF .52

#### 1.3 Modes of Operation

The memory card is capable of operating within the five modes required by the LSI-11 systems as follows:

- A) Read (DATI)

- B) Write (DATO, DATOB)

- C) Read/Modify/Write (DATIO/DATIOB)

- D) Read Block (DATBI)

- E) Write Block (DATBO)

The Read and Block modes operate on the full 16 bit memory word. The Write modes can operate on either the full word (16 bits) or on a byte (8 bits). The memory card provides its own refresh timing and addressing.

## 1.4 Timing

The NS23C access and cycle time characteristics are defined in Table 1

1. Read (DATI) access time is defined as internal SYNC H to RPLY H with

25ns from SYNC H to DIN H. Write (DATO) access time is defined as

internal SYNC H to RPLY H with 50ns from SYNC H to DOUT H. Cycle time is

defined as SYNC H to SYNC H at the maximum speed that the memory will

operate. A delay of up to 500ns can be added to the cycle times if a

memory cycle is requested during a REFRESH operation.

|                       | I BUS CYCLE | IACCESS TIM  | E CYCLE TIME  |

|-----------------------|-------------|--------------|---------------|

| MEMORY FUNCTION       | l TYPE      | (MAX)        | (MAX)         |

| Read                  | DATI        | 50ns         | 450ns         |

| Write                 | DATO(B)     | 50 ns        | 450ns         |

| Read / Modify / Write | DATIO(B)    | 500ns        | 925ns         |

| Read Block            | DATBI       | 50ns         | 450ns         |

| Write Block           | DATBO       | <b>50</b> ns | <b>450</b> ns |

Table 1-1. Access and Cycle Timing

NOTE: Timing values taken at bus receiver outputs and bus driver inputs.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 6 OF . 52

## 1.5 Power Requirements

Table 1-2 shows the power specifications for the NS23C memory module.

| SUPPLY VOLTAGE | 1 | TYPICAL | 1 | MAXIMUM | 1 |

|----------------|---|---------|---|---------|---|

| +5V ± 5%       | 1 | 1.3A    | L | 1.5A    | ١ |

| +5VBB ± 5%     | 1 | 1.0A    | 1 | 1.1A    | ١ |

Table 1-2. Power Requirements

## 1.6 Mechanical Description

The NS23C is a "Dual" size module and conforms to the "Quad High" DEC backplane specification. The memory card is completely contained on one multilayer printed circuit board and is designed to plug directly into standard LSI-11 backplane/cardguide assemblies and the DDV11-B ("Hex") expansion unit.

#### -- CAUTION --

## 1.7 Dimensions

Table 1-3 illustrates the dimensions of the NS23C memory module.

| ١ | PCB Thickness         | ۱ | .056  | Inches |

|---|-----------------------|---|-------|--------|

| ١ | PCB Width             | ١ | 5.187 | Inches |

| ١ | PCB Length            | 1 | 8.93  | Inches |

| ١ | Max. Component Height | ١ | .375  | Inches |

| ١ | Total Thickness Max.  |   | .490  | Inches |

Table 1-3. Dimensions

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

D

52

SCALE

SHEET 7 OF

## 1.8 Environmental Specifications

The NS23C memory card will operate under the following environmental conditions:

Temperature = 0° to 55°C

Humidity = 10% to 90%

(No condensation)

## 1.9 Reliability and Maintainability

The NS23C was designed to the best commercial standards of workmanship. Reliable service is ensured by a high degree of testing conducted over the operating temperature spectrum.

The maintainability of the NS23C is enhanced by the facts that no timing adjustments are required and all RAMS are installed in sockets for easy field failure replacement.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

0

SCALE

SHEET 8 OF 52

## CHAPTER II THEORY AND OPERATION

## 2.0 General

This section describes the theory and operation of the NS23C memory module in the LSI-11 system.

## 2.1 Interface Specification

## Bus Receivers

Input Low Voltage

Input High Voltage

1.3V Maximum

1.7V Minimum

Maximum input current when connected to 3.8V is 80uA even if no power is applied.

## Bus Drivers

Output low voltage when sinking 70mA is .7V maximum.

Output high leakage current when connected to 3.8V is 25uA even if no power is applied.

## 2.2 Interface Signals

Table 2-1 lists the input control signals.

| Ī | SIGNAL NAME |   | CONNECTOR PIN | _ |

|---|-------------|---|---------------|---|

| 1 | BDOUT L     | 1 | AE2           | ١ |

| ١ | BDIN L      | 1 | AH2           | 1 |

| ı | BSYNC L     | 1 | AJ2           | I |

| ١ | BWTBT L     | ١ | AK2           | ١ |

| ١ | BBS7 L      | ١ | AP2           | J |

| 1 | BDCOK H     | ١ | BA1           | ١ |

| ı | BINIT L     | 1 | AT2           | _ |

Table 2-1. Input Control Signals

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

A

420010105-001

D

SCALE

SHEET 9 OF 52

The NS23C memory presents one standard bus load to the LSI-11 bus for each signal.

## 2.2.1 Control Signal Description

\* BDOUT L (AE2)

This signal, when asserted, indicates that valid data is available on BDALO-15 and that an output transfer is taking place.

#### \* BDIN L (AH2)

This signal, when asserted along with BSYNC, indicates that an input transfer is taking place and that the selected slave device is required to respond by asserting BRPLY and placing data on BDAL 0-15.

#### \* BSYNC L (AJ2)

This signal, when asserted, indicates that a valid address is on the bus. When the address is in the operating range of the memory module, BSYNC will also initiate a memory cycle. The type of memory cycle will be determined by BDIN, BDOUT and BWTBT. BSYNC will remain asserted until the transfer is completed.

If BBS7 is asserted, then a CSR Read or Write cycle will occur if CSR address recognition occurred.

#### \* BWTBT L (AK2)

This signal, when asserted during the leading edge of BSYNC, indicates a write cycle (DATO, DATBO, or DATOB) is to be executed. If asserted during the duration of BDOUT, a byte write (DATOB or DATIOB) will take place. The byte to be written is determined by the state of BDALO during the leading edge of BSYNC. BDALO = 0 indicates byte 0; BDALO = 1 indicates byte 1.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

#### \* BBS7 L (AP2)

This signal, when asserted during the leading edge of BSYNC indicates an I/O operation is requested. If address bits 1-12 match the CSR address, then a CSR read or write cycle will occur. During DATBI transfers, the bus master asserts this signal with the first data transfer until the last transfer to indicate to the slave that there will be subsequent transfers.

### \* BDCOK H (BA1)

This signal goes active high 3ms min. after DC is applied. It falls low 5us min. before DC voltages are out of tolerance.

It prevents the memory card from being selected during power-up or power-down sequences or while in the battery back-up mode.

#### \* BINIT L (AT2)

This signal is used to reset the CSR register.

## 2.2.2 Output Signal Description

Table 2-2 lists the output control signals.

|    |              |   |               | _ |

|----|--------------|---|---------------|---|

| 1_ | SIGNAL NAME  |   | CONNECTOR PIN | _ |

|    | PARERR       | ı | AC1 (BDAL 16) | 1 |

| 1  | ERROR ENABLE | ١ | AD1 (BDAL 17) | 1 |

| ı  | BRPLY L      | 1 | AF2           | ١ |

| 1_ | BREF L       |   | AR1           | _ |

Table 2-2. Output Control Signals

## \* PARERR (AC1, BDAL16)

BDAL 16 is used to indicate memory parity error.

## \* ERROR ENABLE (AD1, BDAL 17)

BDAL 17 is the memory error ENABLE line.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

**SHEET** 11 **OF** 52

## \* BRPLY L (AF2)

This signal is asserted in response to a memory cycle request.

During write cycles (DATO,DATBO,DATIO), RPLY indicates acceptance of data from the bus. During read cycles, (DATI, DATBI,DATIO), RPLY indicates that valid data will be on the bus within 125ns and will remain until RPLY is negated.

#### \* BREF L

This signal is used by the slave device to indicate to the master if it can accept any more transfers in the block mode. By negating it during RPLY Time indicates that no more transfers can be accepted during the present block mode transfer.

## 2.2.3 Extended Address Lines

Table 2-3 shows the extended address signals. If used, they are decoded in the Address selection circuity of the NS23C.

| 1 | SIGNAL NAME |   | CONNECTOR PIN | _ |

|---|-------------|---|---------------|---|

| 1 | BDAL 18 L   | 1 | BC1           | ١ |

| ١ | BDAL 19 L   | 1 | BD1           | ١ |

| ı | BDAL 20 L   | ١ | BE1           | ١ |

| ١ | BDAL 21 L   | 1 | BF1           | _ |

Table 2-3. Extended Address Signals

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

P

SCALE

SHEET 12 OF

#### 2.2.4 Bidirectional Signals

The bidirectional signal lines provide the memory card with address and data information and are illustrated in Table 2-4.

| _  |             |   |               | _ |

|----|-------------|---|---------------|---|

| _  | SIGNAL NAME |   | CONNECTOR PIN | _ |

| 1  | BDAL O L    | 1 | AU2           | I |

| ı  | BDAL 1 L    | 1 | AV2           | ı |

| 1. | BDAL 2 L    | I | BE2           | I |

| 1  | BDAL 3 L    | 1 | BF2           | ı |

| I  | BDAL 4 L    | ١ | BH2           | ١ |

| 1  | BDAL 5 L    |   | ВЈ2           | I |

| 1  | BDAL 6 L    | ١ | BK2           | ١ |

| 1  | BDAL 7 L    | I | BL2           | ١ |

| 1  | BDAL 8 L    | 1 | BM2           | 1 |

| 1  | BDAL 9 L    | I | BN2           | 1 |

| 1  | BDAL 10 L   | I | BP2           | 1 |

| 1  | BDAL 11 L   | ı | BR2           | ١ |

| 1  | BDAL 12 L   | 1 | BS2           | ١ |

| 1  | BDAL 13 L   | I | BT2           | 1 |

| I  | BDAL 14 L   | ı | BU2           | ١ |

| 4  | BDAL 15 L   | 1 | BV2           | ١ |

| 1  | BDAL 16 L   | 1 | AC1           | ١ |

| I_ | BDAL 17 L   |   | AD1           | I |

Table 2-4. Bidirectional Signals

These lines are time-multiplexed between the address and data in/out during any externally requested memory cycle. The NS23C interprets the information on these bidirectional lines to be an address if it occurs -75 to +25ns around the leading edge of BSYNC. At all other times the signals are translated to be either data into or data out of the card.

## 3 I/O Connector Pin List

The I/O connector pin list for the NS23C memory card is given in Table 2-5.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

**SHEET** 13 **OF** .52

| Component Side | Pin         |   | Pin       | Solder Side |

|----------------|-------------|---|-----------|-------------|

|                |             | 1 |           | 1           |

| A Connector    |             | 1 |           | 1           |

| 1              | <b>A1</b>   | ı | A2        | +5 Volts    |

| 1              | B1          | 1 | B2        | 1           |

| BDAL16 L       | <b>C1</b> . | ı | C2        | Ground      |

| BDAL17 L       | D1 💮        | ١ | D2        |             |

|                | E1          | i | E2        | BDOUT L     |

| 1              | F1          | 1 | F2        | BRPLY L     |

| 1              | H1          | 1 | H2        | BDIN L      |

| Ground         | J1          | ı | J2        | BSYNC L     |

| 1              | K1          | 1 | K2        | BWTBT L     |

| 1              | L1          | 1 | L2        | 1           |

| Ground         | M1          | 1 | M2        | BIAKI L     |

| 1              | N1          | 1 | N2 .      | BIAKO L     |

| 1              | P1          | 1 | P2        | BBS7 L      |

|                | . R1        | 1 | R2        | BDMGI L     |

| I BREF L       | <b>S1</b>   | 1 | <b>S2</b> | BDMG0 L     |

| Ground         | T1          | ı | <b>T2</b> | BINIT L     |

| 1              | U1          | 1 | U2        | BDALOO L    |

| 1 .            | <b>V</b> 1  | 1 | V2        | BDALO1 L    |

|                |             |   |           |             |

Table 2-5. I/O Connector Pin List

A

420010105-001

D

SCALE

SHEET 14 OF 52

| Component Side | Pin        |     | Pin  | Solder Side | İ |

|----------------|------------|-----|------|-------------|---|

|                |            | 1   |      |             | İ |

| B Connector    |            | 1   |      |             |   |

|                |            | 1   |      |             |   |

| BDCOK H        | <b>A1</b>  | 1   | A2   | +5V Volts   | I |

| 1              | B1         | . 1 | B2   | !           | 1 |

| BDAL18L        | C1 ·       | ١   | C2   | Ground      | I |

| BDAL19L        | D1 `       | ١   | D2   |             | 1 |

| BDAL20L        | E1         | 1   | E2   | BDALO2 L    | 1 |

| BDAL21L        | F1         | •   | F2   | BDALO3 L    |   |

| 1              | H1         | I   | H2   | BDALO4 L    | ١ |

| Ground         | J1         | 1   | J2   | BDALO5 L    | I |

|                | <u>K</u> 1 | ı   | K2   | BDALO6 L    | I |

| 1              | L1         | 1   | L2   | BDAL07 L    | ١ |

| Ground         | M1         | ı   | M2 · | BDALO8 L    | ١ |

| 1              | N1         | 1   | N2   | BDAL09 L    | 1 |

| 1              | P1         | 1   | P2   | BDAL10 L    | ١ |

| 1              | R1         | 1   | R2   | BDAL11 L    | l |

| 1              | <b>S</b> 1 | 1   | 52   | BDAL12 L    | ١ |

| Ground         | T1         | 1   | T2   | BDAL13 L    | ١ |

| 1              | U1         | 1   | U2   | BDAL14 L    | ١ |

| +5 Volts       | V1         | 1   | V2   | BDAL15 L    | I |

| 1              |            | 1   |      |             | ١ |

Table 2-5 (Cont.) I/O Connector Pin List

## 2.4 Timing

Timing for the NS23C is provided by a 200ns delay line which is triggered by the read/write and refresh flip-flops.

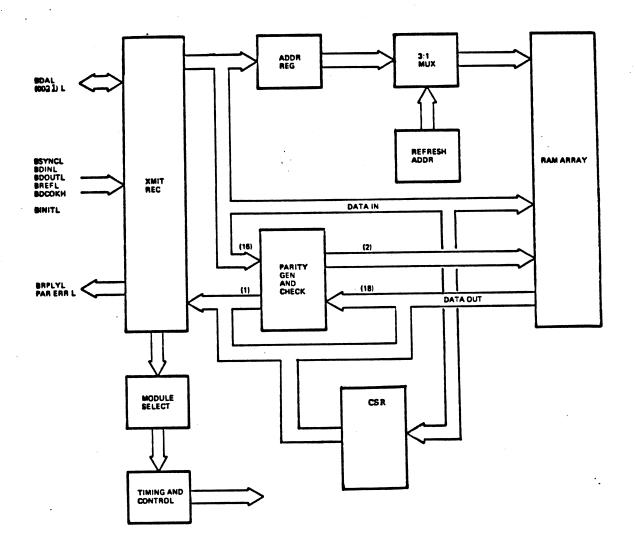

Figures 2-1 through 2-5 depict the data transfer operations of the NS23C. A block diagram of the NS23C is represented by Figure 2-6, and Figure 2-7 indicates the external refresh timing waveform.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

D

SCALE

SHEET 15 OF 52

#### NOTES:

- 1. Timing shown at Bus Driver Inputs and Bus Receiver Outputs

- 2. Signal name prefixes are defined below:

- T. Bus Driver Input

- R. Bus Receiver Output

- 3. Don't care condition

- 4. All timing given in nanoseconds.

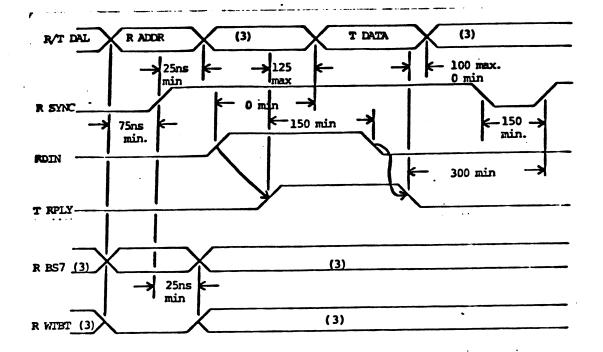

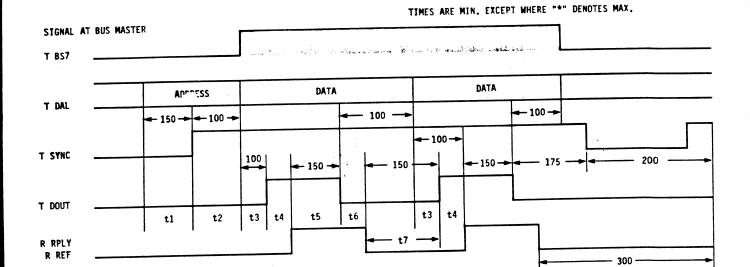

Figure 2-1 - DATI Bus Cycle Timing (Read)

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 16 OF 52

NOTE:

- 1. Timing shown at Bus Driver inputs and Bus Receiver Outputs.

- Signal name prefixes are defined below:

- T. Bus Driver input

- R. Bus Receiver Output

- 3. Don't care condition

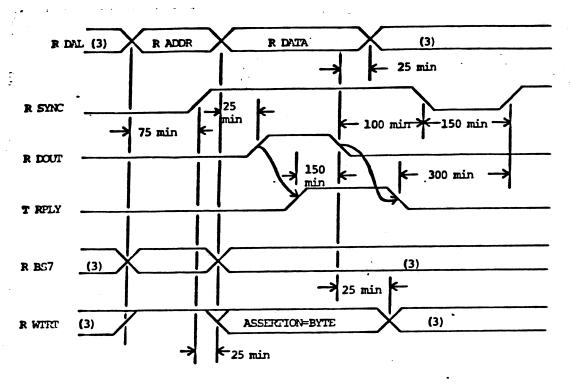

Figure 2-2 - DATO, DATOB Bus Cycle Timing (Write, Write/Byte)

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 17

52

#### NOTE:

- 1. Timing shown at Bus Driver Inputs and Bus Receiver Outputs

- Signal name prefixes are defined below:

- T. Bus Driver Input

- R. Bus Receiver Output

- 3. Don't care condition

- 4. All timings are given in nanoseconds

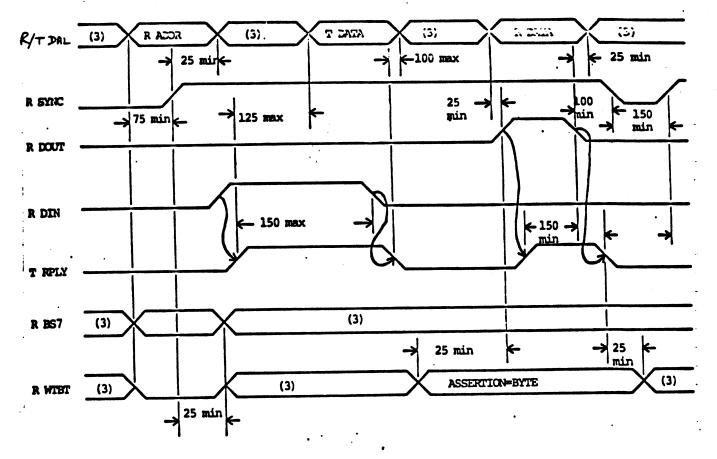

Figure 2-3 - DATIO and DATIOB Bus Cycle Timing (Read-Modify-Write)

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

52

SCALE

SHEET 18

OF

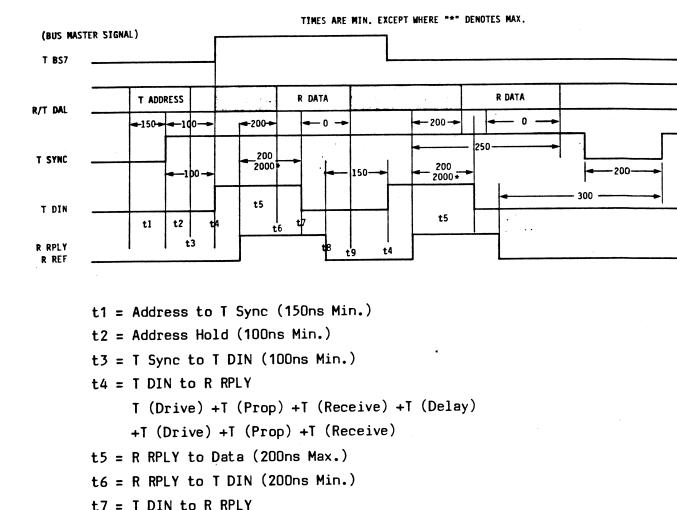

T (Drive) +T (Prop) +T (Receive) +T (Delay)

+T (Drive) +T (Prop) +T (Receive)

t8 = R RPLY to Data (Ons Min.)

Figure 2-4 - DATBI Bus Cycle Timing (Read Block)

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 19

F 52

```

t1 = Address to T Sync (150ns Min.)

(100ns Min.)

t2 = Address Hold

(100ns Min.)

t3 = Data to T DOUT

t4 = T DIN to R RPLY

T (Drive) +T (Prop) +T (Receive) +T (Delay)

+T (Drive) +T (Prop) +T (Receive)

(150ns Max.)

t5 = R RPLY to T DOUT

t6 = T DOUT to R RPLY

= T (Drive) +T (Prop) +T (Receive) +T (Delay)

+T (Drive) +T (Prop) +T (Receive)

(150ns Min.)

t7 = R RPLY to T DOUT

T Cell = t3+t4+t5+t6+7 - Since t3<t7

```

Figure 2-5 - DATBO Bus Cycle Timing (Write Block)

A

420010105-001

D

SCALE

SHEET 20 OF 5

Figure 2-6 Block Diagram

A

420010105-001

D

SCALE

SHEET 21 OF 52

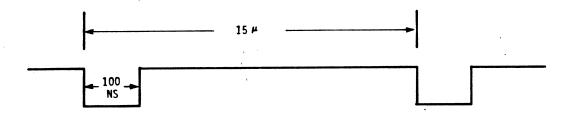

Figure 2-7 External Refresh Timing

A

420010105-001

D

SCALE

SHEET 22

**OF** 5

## 2.5 Memory Card Options

The NS23C memory module contains the following options:

- A) On-board Parity Generation and Checking (CSR)

- B) Extended Address Space Operation

- C) Reserved I/O Space

- D) Block Mode Transfers

- E) Battery Backup

## 2.5.1 Parity Generation and Checking

Provisions have been made on the card for On-board parity generation and checking. A parity bit, plus a parity generator and checker is added per byte. Parity is generated on a byte basis on all write cycles (DATO). Parity is checked on all read cycles (DATI) on a byte basis.

Indication of a parity error on either byte is provided by a parity error signal gated onto the BDAL16 L and BDAL17 L bus lines, which is read by the processor during the memory read DATI cycle.

The parity circuitry can be functionally checked by setting CSR Bit 2 which causes incorrect parity during a DATO cycle and checking the resulting parity error signal during a subsequent DATI cycle at the same address.

A red LED near the module handle indicates that a parity error has occurred.

## 2.5.2 Extended Address Space

The NS23C is capable of operating with 18 bit addressing or 19, 20, 21 or 22 Bit (extended) addressing. Refer to Table 3-5 for jumper settings.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 23 OF 52

#### 2.5.3 Reserved I/O Space

On-board I/O page selection can be configured for 1KW, 2KW or 4KW. Refer to Table 3-6 for jumper placement. Bus Bank Select Seven (BBS7 L) deselects memory during I/O operations and determines if CSR address selection occurs.

#### 2.5.4 Block Mode Transfers

This function allows up to a maximum of 16 data transfers for one address translation. The NS23C contains the counter and necessary circuitry for Block Mode control. Block Mode operation can only be performed on full (16 bit) words. Note: The LSI-11 and LSI-11/2 do not have Block Mode capability and therefore cannot utilize Block Mode transfers.

### 2.5.5 Battery Backup

This optional feature can be utilized in LSI-11 systems where a battery backup system for the semiconductor memory has been implemented by the user. The +5V battery backup voltage pins on the NS23C are compatible with DEC memory specifications. Table 3-6 shows the jumpers associated with battery backup.

## 2.6 Control and Status Register

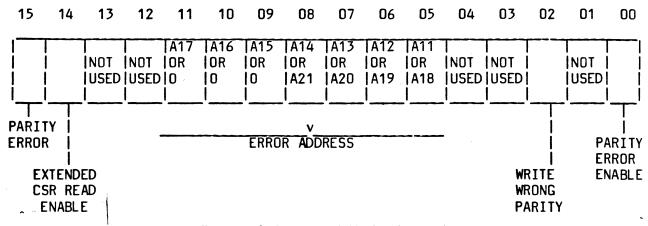

The NS23C Control and Status Register (CSR) allows program control of certain parity functions and contains diagnostic information if a parity error has occurred. The CSR is assigned a Q-Bus address and can be acessed by a bus master. Figure 2-8 illustrates the CSR bit assignment and a description of each bit follows.

Figure 2-8 - CSR Bit Assignment

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 24 OF 52

Bits 1,3,4

Not Used

12,13

These bits are not used and are always read as logical 0's. Writing into these bits has no effect on the CSR.

Bit 0

Parity Error Enable

If a parity error occurs during a DATI, DATBI, DATIO(B) cycle, and bit O is set to a 1, then BDAL 16 and BDAL 17 will be asserted on the bus simultaneously with data. This is a read/write bit reset to zero by INIT L.

Bit 2

Write Wrong Parity

If this bit is set to 1 and a DATO, DATBO, DATIO, DATIOB or DATOB cycle to memory occurs, wrong parity data will be written into the parity RAMs. This bit may be used to check the parity error logic as well as failed address information in the CSR. Bit 2 is a read/write bit reset to zero by INIT L.

Bits 05-11

Error Address

If a parity error occurs on a DATI, DATBI or DATIO(B) cycle, then A11-A17 are stored in CSR bits 5-11 and bits A18-A21 are latched. CSR bit 14 = 0 allows the logic to pass A11-A17 to the LSI-11 bus. CSR bit 14=1 places A18-A21 in CSR bits 5-8.

The parity error address locates the parity error to a 1K segment of memory. These are read/write bits and are not reset by INIT L. If a second parity error is encountered, the new failed address will be stored in the CSR.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 25 OF

Bit 14

Extended CSR Read Enable

When bit 14 is set to a 0, either the read/write register (if no parity errors have been detected) or the contents of the primary error address register (containing A11-A17) can be read on CSR bits 05-11. When bit 14 is set to a 1, the contents of the backup address register will be read on CSR bits 05-11.

Bit 15

Parity Error Indication

If a parity error occurs on a DATI or DATIO(B) cycle, this bit will be set to a 1. This is a read/write bit and is reset to 0 by BUS INII.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

A

420@10105-001

D

SCALE

SHEET 26 OF 52

## CHAPTER III INSTALLATION

## 3.0 General

This chapter contains the basic information necessary for installing the NS23C memory card into DEC LSI-11 compatible systems.

## 3.1 Tools Required

No special tools are required for installation. However, a pair of needle nose pliers will aid in installing or removing the slip-on configuration jumpers.

## 3.2 Unpacking and Inspection

Carefully unpack the memory module and visually examine for damage, especially broken, bent or dented parts.

-- CAUTION --

DO NOT ATTEMPT TO INSTALL OR OPERATE | MEMORY IF PHYSICAL DAMAGE IS APPARENT. | CONTACT NATIONAL SEMICONDUCTOR FOR INFORMATION.

## 3.3 System Verification

All system exercisers should be run to verify system integrity prior to NS23C installation. Any problems should be noted and corrected before proceeding with the installation of the memory card.

## 3.4 Starting Address Selection

The starting address of the NS23C can be set to any 4KW boundary within either the LSI-11 128KW or 2,048KW address range. Refer to Table 3-1 for starting addresses in the 128KW range. For starting addresses in the

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 27 OF ... 52

2,048KW range, Table 3-2 must also be used. When selecting a starting address in the 2,048KW range, extended addressing must be configured on the NS23C and available on the CPU bus. Jumpers W47-50 control extended address selection. Refer to Table 3-5 for placement.

Refer to Figure 3-1 for the NS23C assembly drawing which details the jumper placement.

## 3.5 Memory Size Selection

The memory size of the NS23C may be set from a minimum of 8KW to a maximum of 128KW in 8KW increments. Refer to Table 3-4 for jumper assignments.

### 3.6 CSR Address Selection

The Control and Status Register (CSR) on the NS23C can be assigned to one of eight locations, from 17772100 to 17772116. Refer to Table 3-3 for jumper settings. The CSR may be enabled by installing W27 and removing W28.

## 3.7 I/O Page Size Selection

Jumpers W36 and W37 control I/O page size. Refer to Table 3-6 for the correct setting of these jumpers.

## 3.8 Parity Detection

Parity can be disabled by installing W35 which will inhibit parity enable (BDAL 17) from being asserted when a parity error is detected. This function is independent of the CSR parity functions and will override the CSR. Refer to Table 3-6.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 28

#### Internal/External Refresh 3.9

Either internal or external refresh may be selected on the NS23C. In standard LSI-11 systems internal refresh should be selected. Refer to Table 3-6 for jumper placement.

## 3.10 Battery Back-Up

Battery back-up may be installed on the NS23C in systems where a battery back-up system has been implemented by the user. Refer to Table 3-6 for jumper placement.

## 3.11 Block Mode

Block Mode transfers may be implemented for those systems capable of supporting this feature. Refer to Table 3-6 for jumper selection.

-NOTE-

Older DEC LSI Systems that incorporate the LSI-ll or LSI-11/2 processors do NOT support Block Mode transfers. The NS23C Block Mode feature must be disabled if it is installed in one of these systems.

**National Semiconductor Corporation** 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

SCALE

SHEET 29

2900 Semiconductor Drive Santa Clara, California 95051

SCALE

420010105-001

SHEET 30 OF 52

# Starting Address Selection Table 3-1

| STARTING                     |     |          | JUMF     | ERS**    |               |

|------------------------------|-----|----------|----------|----------|---------------|

| ADDRESS*                     | W10 | W11      | W12      | W13      | W14           |

|                              |     |          |          |          |               |

| OK W                         | 0   | 0        | 0        | 0        | 0             |

| 4K <b>W</b>                  | Ι   | , O      | 0        | 0        | 0             |

| 8K <b>W</b>                  | 0   | · I      | 0        | 0        | 0             |

| 12K <b>W</b>                 | I   | I        | 0        | 0        | 0             |

| 16K <b>W</b>                 | 0   | 0        | <u>I</u> | 0        | <del></del> i |

| 20K <b>W</b>                 | I   | 0        | I        | 0        | ן ס           |

| 24K <b>W</b>                 | 0   | I        | I        | 0        | 0             |

| 28K <b>W</b>                 | · I | I        | I        | 0        | 0             |

| 32K <b>W</b>                 | 0   | 0        | 0        | <u>I</u> | 0             |

| 36K <b>W</b>                 | I   | Ö        | Ö        | Ī        | 0             |

| 40K <b>W</b>                 | Ô   | Ĭ        | Ö        | Ī        | 0             |

| 44K <b>W</b>                 | Ĭ   | Ī        | Ö        | Ī        | 0             |

| 44100                        | •   | <u>-</u> |          |          |               |

| 48K <b>W</b>                 | 0   | 0        | I        | Ī        | 0             |

| 52K₩                         | Ι   | 0        | I        | I        | 0             |

| 56K <b>W</b>                 | 0   | I        | I        | I        | 0             |

| 60K <b>W</b>                 | Ι   | Ι        | I        | I        | 0             |

| 64K <b>W</b>                 | 0   | 0        | 0        | 0        | I             |

| 68K <b>W</b>                 | I   | 0        | 0        | 0        | I             |

| 72K <b>W</b>                 | 0   | I        | 0        | 0        | I             |

| 76K <b>W</b>                 | I   | I        | 0        | 0        | I             |

| 00//1                        | 0   | 0        | Ī        | 0        | —— <u> </u>   |

| 80KN                         | I   | 0        | I        | 0        | Ī             |

| 84K <b>W</b>                 | 0   | I        | Ī        | 0        | Ī             |

| 88K <b>W</b><br>92K <b>W</b> | I   | I        | I        | 0        | Ī             |

| 74K <b>y</b> w               | 1   | 1        | 1        | U        | •             |

| 96K <b>W</b>                 | 0   | 0        | 0        | Ī        | Ī             |

| 100K <b>W</b>                | I   | 0        | 0        | I        | I             |

| 104K <b>W</b>                | 0   | I        | 0        | I        | I             |

| 108K <b>W</b>                | I   | I        | 0        | I        | I             |

| 112K <b>W</b>                | 0   | 0        | I        | Ī        | Ī             |

| 116K <b>W</b>                | Ī   | 0        | I        | I        | I             |

| 120K <b>W</b>                | Ō   | I        | I        | I        | I             |

| 124K <b>₩</b>                | I   | I        | I        | I        | I             |

|                              |     |          |          |          |               |

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 31

**OF** 52

| ADDRESS                    |                                | JUM | PERS* |     |

|----------------------------|--------------------------------|-----|-------|-----|

| RANGE                      | W15                            | W16 | W17   | W18 |

| l                          |                                |     |       |     |

| 0 −128K <b>W</b>           | 0                              | 0   | 0     | 0   |

| 128 <b>–</b> 256K <b>₩</b> | I                              | 0   | 0     | 0   |

| 256 <b>–3</b> 84K <b>₩</b> | 0                              | I   | 0     | 0 1 |

| 384 -512K₩                 | I                              | I   | 0     | 0   |

|                            |                                |     |       |     |

| 512 -640KW                 | 0                              | 0   | I     | 0 1 |

| 640 <b>-</b> 768K <b>₩</b> | $\cdot \cdot \cdot \mathbf{I}$ | 0   | I     | 0   |

| 768 -896K <b>₩</b>         | . 0                            | I   | Ι     | 0   |

| 896 -1024K₩                | I                              | I   | I     | 0 1 |

|                            |                                |     |       |     |

| 1024 −1152K₩               | 0                              | 0   | 0     | I   |

| 1152 −1280K <b>W</b>       | I                              | 0   | 0     | I   |

| i 1280 −1408K <b>W</b>     | 0                              | I   | 0     | I   |

| 1408 -1536KW               | I                              | I   | 0     | I   |

|                            |                                |     |       | [   |

| 1536 -1664KW               | 0                              | 0   | Ī     | I   |

| 1664 −1792K <b>W</b>       | I                              | 0   | I     | I   |

| 1792 -1920K <b>₩</b>       | 0                              | I   | I     | I   |

| 1920 -2048KW               | I                              | I   | I     | I   |

|                            | _                              | •   |       |     |

## Address Range Selection Table 3-2

| 22 Bit   | 18 Bit  |      | JUMPERS* |    |

|----------|---------|------|----------|----|

| CSR      | CSR     | : W9 | w8       | W7 |

| Address  | Address | -    |          |    |

| 17772100 | 772100  | I    | Ī        | Ī  |

| 17772102 | 772102  | 0    | I        | I  |

| 17772104 | 772104  | I    | 0        | I  |

| 17772106 | 772106  | 0    | 0        | I  |

| 17772110 | 772110  | I    | I        | 0  |

| 17772112 | 772112  | 0    | I        | 0  |

| 17772114 | 772114  | I    | 0 .      | 0  |

| 17772116 | 772116  | 0    | 0        | 0  |

\* 0 = Remove I = Install

> CSR Address Selection Table 3-3

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

SHEET 32

Table 3-4. Memory Size

| Maria Maria Maria Maria Maria Maria Maria Maria Maria Maria Maria Maria Maria Maria Maria Maria Maria Maria Ma |              | JUM        | pees*       |            |

|----------------------------------------------------------------------------------------------------------------|--------------|------------|-------------|------------|

| MEMORY<br>SIZE                                                                                                 | W22          | W21        | W2 <b>0</b> | W19        |

| 8KW                                                                                                            | I.           | I          | I.          | I          |

| 16KM                                                                                                           | I.           | <b>T</b> . | Ι.          | O          |

| 24KW                                                                                                           | <b>I</b>     | I          | O           | <b>X</b> . |

| 32KW                                                                                                           | <b>X</b>     | 1          | 0           | <u>(</u> ) |

| 40KW                                                                                                           | T.           | 0          | I           | 1          |

| 48KW                                                                                                           | $\mathbf{I}$ | O          | X           | O          |

| 56KW                                                                                                           | I.           | 0          | O           | 1          |

| 64KW                                                                                                           | Ĭ            | 0          | 0           | <u> </u>   |

| 72KW                                                                                                           | 0            | T          | Ι.          | I          |

| 80KW                                                                                                           | Ö            | 1          | <b>X</b> :  | O          |

| 88KW                                                                                                           | 0            | <b>X</b>   | O           | I          |

| 96KW                                                                                                           | Ö            | 1          | 0           | ()         |

| 1.04KW                                                                                                         | 0            | <u>C)</u>  | I.          | 1.         |

| L1.2KW                                                                                                         | O            | O          | I           | O          |

| 120KW                                                                                                          | O            | O          | 0           | 1.         |

| 128KW                                                                                                          | 0            | 0          | O           | O          |

Table 3-5. Extended Address Selection

| 1            |      | JUMPE | R5*~~~~ |     |

|--------------|------|-------|---------|-----|

| ADDRESS TYPE | W47_ | W48   | W49     | W50 |

| 18-bit       | 0    | 0     | 0       | 0   |

| 19-bit       | I    | 0     | 0       | 0   |

| 20-bit       | I    | I     | 0       | 0   |

| 21-bit       | I    | I     | 0       | I   |

| 22-bit       | I    | I     | I       | I   |

0 = Remove

I = Install

**National Semiconductor Corporation** 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

D

33 OF ... 52

# Jumper Definitions Table 3-6

| JUMPER    | PURPOSE                | CONFIGURATION                                                      |

|-----------|------------------------|--------------------------------------------------------------------|

| <b>W1</b> | Battery Backup         | I = Non battery backup R = Battery backup                          |

| W2        | Battery Backup         | <pre>I = Battery backup R = Non battery backup</pre>               |

| W3        | Refresh                | <pre>I = Internal refresh R = External refresh</pre>               |

| W4        | Refresh                | <pre>I = External refresh R = Internal refresh</pre>               |

| W5        | Refresh                | <pre>I = BREF L inhibit select R = BREF L not inhibit select</pre> |

| <b>W6</b> | Refresh                | <pre>I = BREF L not inhibit select R = BREF L inhibit select</pre> |

| W7-W9     | CSR Address            | See Table 8-5                                                      |

| W10-W18   | Start Addr Select      | See Table 8-2 and 8-3.                                             |

| W19-W22   | Memory Size Select     | See Table 8-4.                                                     |

| W23-W24   | Factory Installed - Do | Not Alter                                                          |

| W27       | CSR Enable             | <pre>I = CSR enabled R = CSR disabled</pre>                        |

| W28       | CSR Disable            | <pre>I = CSR disable R = CSR enable</pre>                          |

| W29       | NOT USED               |                                                                    |

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

SCALE

SHEET 34 OF 52

## Jumper Definitions (Cont.)

## Table 3-6

| JUMPER      | PURPOSE                    | CONFIGURATION                                           |

|-------------|----------------------------|---------------------------------------------------------|

| <b>W</b> 30 | Block Mode Disable         | I = Block Mode Disable<br>R = Block Mode Enable         |

| W31         | Block Mode Enable          | I = Block Mode Enable<br>R = Block Mode Disable         |

| W32         | Factory Test Only          | Remove                                                  |

| W33         | Factory Test Only          | Install                                                 |

| W34         | Factory Test Only          | Remove                                                  |

| W35         | Parity                     | I = Parity Enable Disabled<br>R = Parity Enable Enabled |

| W36         | I/O Page                   | I = 1KW I/O Page<br>R = 4KW or 2KW I/O Page             |

| W37         | I/O Page                   | I = 1KW or 2KW I/O Page<br>R = 4KW I/O Page             |

| W38-W46     | Factory Configuration Only | - Do Not Alter                                          |

| W47-50      | Extended Address           | See Table 3-5                                           |

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

SCALE

SHEET 35

OF !

## 3.12 Installing the NS23C

- A) Halt the operating system, if running.

- B) Set all peripherals to the "unload" condition.

- C) Turn system power off.

CAUTION

DO NOT ATTEMPT TO INSTALL OR REMOVE

MEMORY MODULES WITH DC POWER APPLIED

TO THE BACKPLANE. DAMAGE TO THE

MEMORY OR OTHER MODULES MAY OCCUR.

- D) Verify jumper configurations for starting address, CSR address, memory size, and other options. Note that all existing system memory must be considered before setting the starting address of the NS23C.

- E) Install memory module carefully into the selected slot. Insure that the component side faces the correct direction and the module is aligned in the card guides. Caution should be taken not to allow components to rub adjacent modules. Press FIRMLY when module engages backplane connectors, and check to be sure module is seated properly.

- F) Turn system power "on".

- G) Run memory diagnostics. Refer to Chapter IV for diagnostic information.

#### \*\*\* NOTE \*\*\*

On systems using the KDJ11 (11/73) CPU, cache must be disabled before any memory diagnostic is run. This is done by depositing 14 in the cache control register (Address 17777746).

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

SCALE

SHEET 36 OF 52

# CHAPTER IV DIAGNOSTICS AND TROUBLESHOOTING

#### 4.1 General

This section describes how to use the DEC memory diagnostics to troubleshoot and isolate a failure in memory to a faulty RAM. Standard XXDP loading and starting procedures are used on processors with no hardware switch registers; the software switch register will be in location 176.

NOTE: The parity LED will turn on and off during diagnostic testing.

#### 4. 2 ZKMA

This diagnostic will test O-256KB of memory on any PDP-11 family computer.

#### SWITCH SETTING SUMMARY

```

HALT ON ERROR

BIT 15(100000); SW15=1

BIT 14(040000); SW14=1 LOOP ON TEST

BIT 13(020000); SW13=1 INHIBIT ERROR PRINTOUTS

BIT 12(010000); SW12=1 ENABLE TESTING ABOVE 28K

BIT 11(004000); SW11=1 ENABLE PARITY TESTING

BIT 10(002000); SW10=1 HALT AFTER EACH TEST

9(001000); SW9 =1 INHIBIT PROGRAM RELOCATION

BIT

TYPE FIRST FAILURE IN 4K BANK

8(000400); SWB = 1

BIT

7(000200); SW7 = 1

LONG GALLOP TEST*

BIT

INHIBIT MEMORY SIZING

6(000100); SW6 =1

BIT

INHIBIT END PASS PRINTOUTS

5(000040); SW5 =1

BIT

INHIBIT PRINTOUTS

4(000020); SW4 = 1

BIT

BEGINNING TEST NUMBER

BIT3-0; SW3-0

```

CAUTION: The LONG GALLOP TEST will increase test times by a factor of 25!

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

SCALE

SHEET 37 OF 52

## 4.3 Running ZKMA

- 1. Load program ZKMA?? into memory (L ZKMA?? <CR>).

- 2. Select options by setting bits into the switch register. Refer to the above switch settings. Note: Normal switch settings would be bits 11 and 12 set (014000).

- Start program testing (S <CR>).

- 4. A pass with no errors detected will appear similar to the following sample printout:

000000-757777

**PARITY**

TST13 BNK D

TST13 BNK 1

TST13 BNK 2

TST13 BNK 3

TST13 BNK 4

TST13 BNK 5

TST13 BNK 6

RELOC

TST13 BNK 0

END PASS 1

5. The following is an example of a typical error message printout:

LOCATION GOOD BAD PC ERROR PASFLG 177210 177777 177776 1625 10 [TSTO]

LOCATION = FAILING MEMORY LOCATION

GOOD = GOOD DATA (DATA THAT WAS EXPECTED)

BAD = BAD DATA (DATA THAT WAS FOUND)

PC = PROGRAM COUNTER AT ERROR CALL

ERROR = FAILING ERROR NUMBER

PASFLG = CONTENTS OF ERROR PASFLG (THIS MAY NOT BE RELEVANT)

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

A

420010105-001

T

SCALE

SHEET 38 OF , 52

Using the above printout as an example, the failure would be found in the address range O-128KB (177210 is between 0 and 377776). failing bit would be zero; this is determined by comparing good data with bad data (177777-177776=000001). With this information available, Figure 4-1 can be used in conjunction with Table 4-1 to isolate and replace the failing RAM. The RAM to be replaced in this example would be U12. The PC, Error and PASFLG information are not normally needed to determine the failing RAM and are not needed in this example. If they are needed, refer to the DEC diagnostic listing for ZKMA.

#### 4.4 ZQMC

This program has the ability to test memory from address 000000 to 757777, (0-248KB of memory), on any PDP-11 family processor.

## SWITCH SETTING SUMMARY

```

HALT ON ERROR

BIT 15(100000); SW15=1

BIT 14(040000); SW14=1

LOOP ON TEST

INHIBIT ERROR PRINTOUTS

BIT 13(020000); SW13=1

INHIBIT MEMORY MANAGEMENT

BIT 12(010000); SW12=1

INHIBIT SUBTEST ITERATION

BIT 11(004000); SW11=1

RING BELL ON ERROR

BIT 10(002000); SW10=1

LOOP ON ERROR

BIT 9(001000); SW9 =1

LOOP ON TEST IN SWR<4:0>

BIT 8(000400); SW8 =1

INHIBIT PROGRAM RELOCATION

BIT 7(000200); SW7 =1

INHIBIT PARITY ERROR DETECTION*

BIT 6(000100); SW6 =1

INHIBIT EXERCISING VECTOR AREA

BIT 5(000040); SW5 =1

BEGINNING TEST NUMBER

BITS 4-0; SW4-0

```

With parity error detection enabled, a memory failure can cause a parity error. The error printout on a parity error does not type the good data. Thus a bit dropped or picked-up will not be typed as such, therefore it is best to run the program for 1 pass with parity disabled then restart the program with parity enabled.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

D

SCALE

OF SHEET 39

#### Running ZQMC 4.5

- Load program ZQMC?? into memory, (L ZQMC?? <CR>). 1.

- Select options by setting bits into the switch register. Refer to 2. the above switch settings. Note: Normal switch settings would be bit 6 set for the first pass (000100), and no bits set for the second pass (000000).

- Start program testing, (S <CR>). 3.

- If there are no errors detected the printout will appear similar to 4. the following format:

KT11 (MEMORY MANAGEMENT) AVAILABLE

MEMORY MAP:

FROM 000000 TO 757777

PARITY MEMORY MAP:

REGISTER AT 172100 CONTROLS

FROM 000000 TO 757777

PROGRAM RELOCATED TO 720000

PROGRAM RELOCATED TO 000000

END PASS #1

There is a total of 31 types of error reports generated by this 5. program. Some of the key column heading mnemonics are described below for clarity:

= PROGRAM COUNTER OF ERROR DETECTION CODE. PC

= VIRTUAL PROGRAM COUNTER. THIS IS WHERE THE ERROR DETECTION V/PC CODE CAN BE FOUND IN THE PROGRAM LISTING.

= PHYSICAL PROGRAM COUNTER. THIS IS WHERE THE ERROR P/PC DETECTION CODE IS ACTUALLY LOCATED IN MEMORY.

TRP/PC = PHYSICAL PROGRAM COUNTER OF THE CODE WHICH CAUSED A TRAP.

= MEMORY ADDRESS MA

REG = PARITY REGISTER ADDRESS

PS = PROCESSOR STATUS WORD

= INSTRUCTIONS UNDER TEST IUT

**National Semiconductor Corporation** 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

D

SCALE

SHEET 40

S/B = WHAT CONTENTS SHOULD BE (GOOD DATA)

WAS = WHAT CONTENTS WAS (BAD DATA)

The following is an example of a typical error message printout:

V/PC

P/PC

MA

S/B

WAS

006300

006300

473732

133732

173732

Using the above printout as an example, the failure would be found in the address range 128Kb-256Kb, (473732 is between 004000000 and 00777776). The failing bit would be bit "14"; this is determined by comparing good data with bad data, (S/B with WAS), and doing an EXCLUSIVE OR of the two, (133732-173732)=040000) and locating the bad octal bit, bit "14". Using Figure 4.1, and referencing Table 4-1, the failing RAM is found to be U15. For error messages that do not display the failing address and good/bad data, refer to the DEC diagnostic listing for ZQMC or call National Semiconductor Memory Systems Technical Support.

#### 4.6 ZMSD

This diagnostic can test up to 4MB of memory and can be run on any PDP-11 or LSI-11 computer system with extended (22 bit) Addressing, Control and Status Register (CSR) capabilities, and at least 128KB of memory.

## SWITCH REGISTER OPTIONS

BIT 15(100000); SW15=1 HALT ON ERROR

BIT 14(040000); SW14=1 LOOP ON TEST

BIT 13(020000); SW13=1 INHIBIT ERROR PRINTOUTS

BIT 12(010000); SW12=1 INHIBIT RELOCATION

BIT 11(004000); SW11=1 QUICK VERIFY

BIT 10(002000); SW10=1 RING BELL ON ERROR

BIT 9(001000); SW9 =1 LOOP ON ERROR

BIT 8(000400); SW8 =1 HALT PROGRAM

BIT 7(000200); SW7 =1 DETAILED ERROR REPORT

BIT 6(000100); SW6 =1 INHIBIT CONFIGURATION MAP

BIT 5(000040); SW5 =1 LIMIT MAX ERRORS PER BANK

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D

SCALE

**SHEET** 41 **OF** 52

BIT 4(000020); SW4 =1 FAT TERMINAL (132 COLUMNS PRINTER)

BITS 3-0; SW3-0 TEST MODE

## 4.7 Running ZMSD

- 1. Load program ZMSD into memory (L ZMSD?? <CR>).

- Select options by setting bits in the switch register. Refer to the above switch settings. Normal switch setting would be all bits off (000000).

- Start program testing (S <CR>).

- 4. The program will start running, size memory, and print out a configuration map. The diagnostic will not fully exercise the memory board whose CSR controls the memory containing the diagnostic.

- 5. In the following example, the configuration map printout for ZMSD is for a system with one NS23C memory board installed as the only memory board in the system (the NS23C is set for 256KB of memory).

1 2 3 4 5 6 7 0123456701234567012345670123456701234567012345670123

**ERRORS**

CPU MAP 11111111

INTRLV -----

MEMTYPE LLLLLLL

CSR 00000000

PROTECT PP

#### MEMORY CONFIGURATION MAP EXPLANATIONS

BANKS = EACH BANK EQUALS 16KW OF MEMORY. EIGHT BANKS WOUULD EQUAL 128KW OF MEMORY AND BE READ AS 10 OCTAL BANKS.

ERRORS = IF THE MEMORY SIZING ROUTINE COULD NOT WRITE 1'S AND O'S IN A

BANK, A "X" WOULD BE TYPED FOLLOWING THIS HEADING UNDER THE

FAILING 16K BANK.

National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051 A

420010105-001

D.

SCALE

SHEET 42 OF ... 52

CPU MAP = THE CPU WAS ABLE TO ACCESS THESE BANKS.

INTRLV = IF INTERLEAVED, THE CSR CONTROLLING ADDRESS BIT 1 IS TYPED.

MEMTYPE = MEMORY TYPE, L=MSV11-L, P=MSV11-P

PROTECT = PROGRAM PROTECTED SPACE, WHERE THE DIAGNOSTIC RESIDES,

(INDICATED BY A "P"). NO ERRORS ARE REPORTED IN THESE BANKS.

6. A good pass will print out "END PASS 1" (for first pass).

Error information; the following is an example of a typical memory data error, error header definitions, and troubleshooting steps.

#### SAMPLE ERROR MESSAGE

| PC     | BANK | <b>V</b> ADD   | PADD     | <b>G</b> 00D | BAD    | XOR    | CSR | MTYP | INT | PAT |

|--------|------|----------------|----------|--------------|--------|--------|-----|------|-----|-----|

| 022134 | 7    | <b>0</b> 60060 | 00700060 | 000000       | 010000 | 010000 | 0   | L    | -   | 06  |

| 022134 | 7    | 060060         | 00700060 | 000000       | 010000 | 010000 | 0   | L    | -   | 06  |

| 022134 | 7    | 060060         | 00700060 | 000000       | 010000 | 010000 | 0   | L    | -   | 06  |

| 022134 | 7    | 060060         | 00700060 | 000000       | 010000 | 010000 | 0   | L    | _   | 06  |

#### ERROR HEADER DEFINITIONS

PC = PROGRAM COUNTER

BANK = BANK OF MEMORY UNDER TEST

VADD = VIRTUAL ADDRESS

PADD = PHYSICAL ADDRESS

GOOD = DATA EXPECTED

BAD = DATA RECEIVED

XOR = THE X-ORED VALUE OF THE GOOD AND BAD DATA

CSR = CONTROL AND STATUS REGISTER

INT = INTERLEAVED

PAT = DATA PATTERN USED

7. Listed below are the necessary steps used to troubleshoot and isolate the failing RAM. (Refer to the Sample Error Message).

Determine the bank in memory where the error occurred (BANK 7).

**National Semiconductor Corporation** 2900 Semiconductor Drive Santa Clara, California 95051

420010105-001

SCALE

SHEET 43 52 Locate the PADD (Physical Address) and record its contents (00700060).