Model GT304 Serial I/O Board

### **User Manual**

Model GT304 Serial I/O Board

Original Issue - September 1988

979-0021-304

Price: \$5.00

2900 Gateway Drive Pompano Beach, Florida 33069 Phone (305) 974-5500 TWX 510-956-9895 © 1988 Computèr Products, Inc. Printed In U.S.A.

### MODEL 304

### SERIAL I/O BOARD

### TABLE OF CONTENTS

| Description                                                                                                                                                                                                                                        | Page                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Features General Specifications Q-Bus Interface Interrupt Logic Console Channel UART                                                                                                                                                               | 1<br>1<br>2<br>3<br>3<br>5<br>5<br>6<br>6<br>7<br>7 |

| Control & Status Registers Data Registers Error Registers EIA Circuit Baud Rate Generator                                                                                                                                                          | 6<br>6<br>7<br>7<br>7                               |

| Operation Modes                                                                                                                                                                                                                                    | 8                                                   |

| Factory Configuration Setting the Base Address Setting the Vector Address Setting the Interrupt Level Setting the Baud Rate Enabling the Console System Halt or Reboot Setting the Serial Data Format Setting the Line Discipline Reader Run Pulse | 10<br>10<br>11<br>12<br>13<br>13<br>14<br>15<br>15  |

| Serial Interface                                                                                                                                                                                                                                   | 18                                                  |

| Connector Description Line Discipline, Cable Length & Data Rates                                                                                                                                                                                   | 18<br>19                                            |

| Programming                                                                                                                                                                                                                                        | 20                                                  |

| Warranty                                                                                                                                                                                                                                           | y.                                                  |

### FEATURES

- \* Direct Replacement for DLV11-J Serial I/O Board

- \* Totally Compatible with DEC Software

- \* All Standard DEC Features

- \* Each Port Independently Configured for Either EIA RS-232, RS-422, or RS-423

- \* Four Level Vector Interrupt Structure, Ideal for Multi-User Applications

- \* Channel 3 can be Independently Configured as System Console

### GENERAL

The Model 304 is a four channel serial I/O port for interfacing DEC's Q-bus to asynchronous serial data channels. The 304 is a direct replacement for the DEC four channel Serial I/O Board (Model DLV11-J). It is packaged on the standard 8.9" x 5.2" DEC style dual width board and is electrically and mechanically compatible with DEC's LSI-11, 11/2, and 11/23 Microcomputer Series.

Each channel consists of a UART which receives and converts serial start, data, parity and stop bits to parallel data verifying proper code transmission, parity and stop bits. The UART's transmitter converts the computer's parallel data into serial form and automatically adds start, parity, and stop bits.

Each channel's data length can be configured for 7 or 8 bits. Parity is jumper selectable, odd or even, and parity checking and generation can be inhibited. Stop bits are jumper selectable; one or two.

The 304 can be used in a wide range of interface applications including printers, terminals, peripherals and remote data acquisition systems. Each channel can operate at one of nine jumper selectable data rates, from 150 to 38.4K baud, which are generated by an on-board clock. The user may also provide an external clock.

The line characteristics of each channel can be jumper configured to operate in accordance with EIA standard RS-232,

RS-422, or RS-423. Twenty milliamp current loop operation is possible when used in conjunction with the DEC DLV11-KA.

A unique feature of the 304 is the capability to support the LSI 11/23 four level interrupt structure. Channel 3 may also be configured as the system console, independent of the other three channels. Special pins are provided on each I/O connector which can be used to constantly assert the data terminal ready lines of the peripheral, and each channel can also be configured to provide a pulse output to control a paper tape reader.

### SPECIFICATIONS

Bus Interface Q-bus, DEC LSI-11, 11/2 &

Data Characteristics

(Each Channel)

No. of Channels

Data Protocol

Baud Rates

Line Discipline

Data Bits

Stop Bits

Parity

Addressing

Base Address Range

Console Address

Interrupts

Priority Level

Base Vector Range

Console Vector

11/23 compatible

Asynchronous serial

Jumper Selectable 150, 300, 600, 1.2K, 2.4K, 4.8K, 9.6K, 19.2K 38.4K, Ext.

Jumper Selectable EIA RS-232C,

RS-422, or RS-423

Jumper Selectable 7 or 8

Jumper Selectable 1 or 2

Jumper Selectable Odd, Even,

None

Jumper Selectable 776000g to

777740

Jumper Selectable 777560g

Channel 3 Only

Jumper Selectable LSI-11 & 11/2

Level 4, Jumper Selectable LSI-11/12

Level 4, 5, 6, or 7

Jumper Selectable 0 to 740,

60 only when console option is enabled

2 .

### Mechanical & Environmental

Dimensions DEC LSI-11 standard 8.9" x 5.2"

half quad board

Power Requirements 5V @ 1 Amp, 12V @ .2 Amps

Bus Loading 1.5 Std. AC/1 Std. DC Load

Operating Temperature 0 to 55°C

Range

Storage Temperature 0 to 75°C

Range

Relative Humidity To 85% non-condensing

Mating Connector Amp #87133-5, Pin #87165-2

### Q-BUS INTERFACE

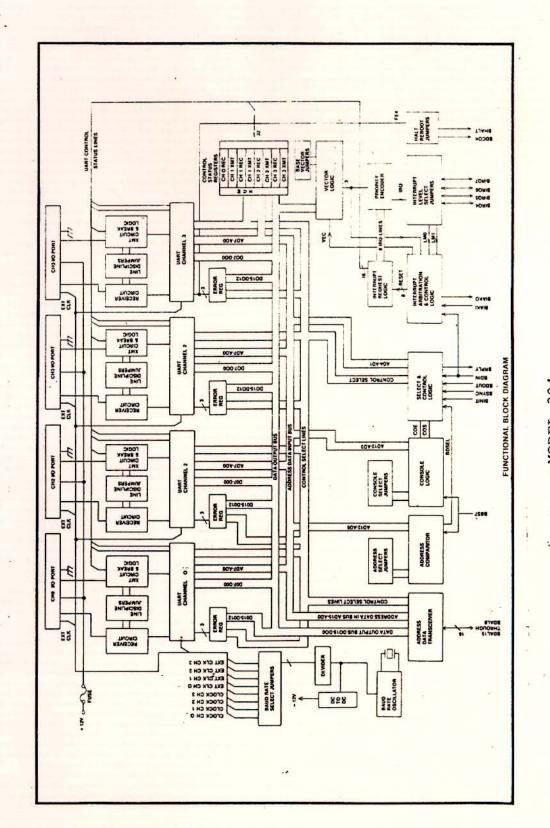

The Q-Bus Interface consists of address/data transceivers, an address comparator, console decode logic and I/O select and control logic.

During the addressing portion of a bus cycle, the Address/Data transceivers are in the receive mode. Address lines 12 through 5, gated by bus line BBS7, are compared to the base address setting selected by the address selection jumpers. When the correct address is asserted by the processor, the comparator output (BDSEL) is asserted. This in conjunction with the assertion of BSYNC is used by the Select and Control Logic (SCL) to select the appropriate on-board register for the remainder of the bus cycle.

If the processor is performing a read, then the BDIN line is decoded in conjunction with the SCL to enable the tristate buffers of the selected register, place the bus transceivers in their transmit mode, and then assert the BRPLY line.

If the processor is performing a write operation, then the register which is to be written to is selected during the Address/Data portion of the bus cycle and the BDOUT line is used to clock the latches of the receiving register, and to assert BRPLY.

### INTERRUPT LOGIC

The interrupt handling logic consists of interrupt request logic, a priority encoder, level circuit logic, arbitration control, and vector logic.

The interrupt request logic consists of eight latches; one for each transmit or receive CSR. In order to generate an interrupt, two requirements must be met. First, the interrupt

MODEL 304 Functional Block Diagram

4

enable bit (Bit 6) in either the transmit or receive CSR must be set, and second, the appropriate condition flag must be set (Bit 7). These two logically anded signals clock the flop. The outputs of all eight flops are fed into the priority encoder. When the output of any flop goes high, the priority encoder generates a master interrupt request (IRQ). This signal is fed into the level select logic which in turn asserts the appropriate BIRQ lines. At the same time the arbitration logic monitors the bus to determine if a device on a higher interrupt level is requesting. If not, then when the interrupt grant signal BIAKI is received, the appropriate vector as determined by the priority encoder is placed on the bus, and if more than one channel is requesting, the channel of highest priority is cleared leaving the lower priority requests pending. Table 1 gives the priority level of each channel.

| Channel |     |          | Level |         |          | Vecto | or Offse | <u>et</u> |

|---------|-----|----------|-------|---------|----------|-------|----------|-----------|

| Channel | 0   | Receive  | 0     | Highest | Priority | Base  | Vector   | + Ø'      |

| Channel | 1 ' | Receive  | 1     |         |          | Base  | Vector   | +10       |

| Channel | 2   | Receive  | 2     |         |          | Base  | Vector   | +20       |

| Channel | 3   | Receive  | 3     |         |          | Base  | Vector   | +30       |

| Channel | 0   | Transmit | 4     |         |          | Base  | Vector   | +4        |

| Channel | 1   | Transmit | 5     |         |          | Base  | Vector   | +14       |

| Channel | 2   | Transmit | 6     |         | ,        | Base  | Vector   | +24       |

| Channel | 3   | Transmit | 7     | Lowest  | Priority | Base  | Vector   | +34       |

### TABLE 1

### CONSOLE CHANNEL

When the console enable jumper is installed, Channel 3 will respond to the address of 1775608, and the receiver will always have a vector address of 608. The transmitter vector will be 648. The console mode of operation is independent of the board's base address.

### UART

Each channel consists of a Universal Asynchronous Receiver Transmitter (UART) which receives and converts serial data, parity and stop bits to parallel data verifying proper code transmission, parity and stop bits. If a transmission error is detected, the nature of the error is outputed to an error register which is read when the receive data register is read. Upon receiving the last stop bit, the receiver full flag is set (Bit 7 of the receive CSR). If the receiver interrupt enable bit is set (Bit 6), then the receiver full flag will generate an interrupt request.

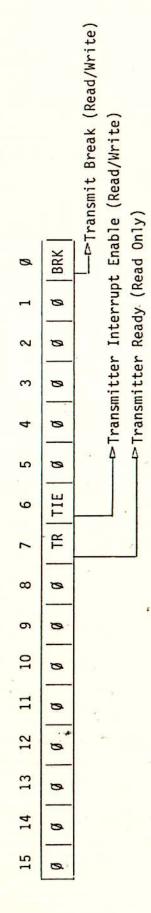

The UART's transmitter converts the computer's parallel data into a serial format and automatically adds start, parity, and stop bits. When the transmitter buffer is ready to receive a byte of data for transmission, the transmitter ready flag is set (Bit 7 of the transmitter CSR). If the transmitter interrupt enable bit is set (Bit 6), then the transmitter ready flag will generate an interrupt.

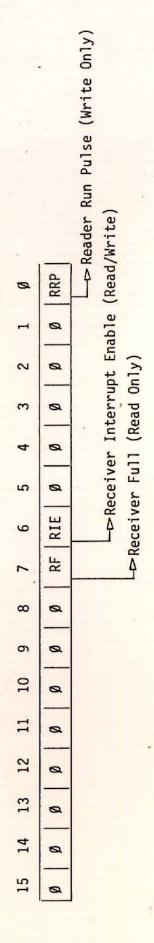

### CONTROL STATUS REGISTER (CSR)

Each channel contains a 16 bit receiver CSR and a 16 bit transmitter CSR. Bit 7 is a read only bit used as a status flag and Bit 6 is a read/write bit used to enable an interrupt request when Bit 7 gets set.

Bit 7 of the receiver CSR is used to indicate that the receiver contains new data. Bit 7 is cleared by reading the receiver's data register or by a software reset. When Bit 6 is set, an interrupt request is generated when Bit 7 is set.

Bit Ø of the receiver CSR is used to transmit a reader run pulse. This bit is a write only bit and always reads zero.

Bit 7 of the transmitter CSR, when set, indicates the transmitter buffer is empty and ready to transmit new data. Setting Bit 6 will generate an interrupt whenever Bit 7 is set.

Bit Ø, when set, will transmit a continuous break.

All unused CSR bits in both the transmitter and receiver CSR's will always read zero.

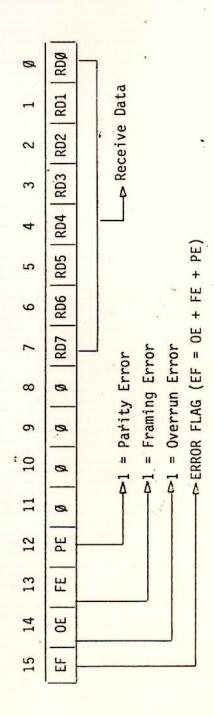

### DATA REGISTERS

Each channel contains a Receiver Data Register (RDR) and a Transmitter Data Register (TDR). When data is received, it is placed in the RDR and Bit 7 of the Receiver CSR is set. The received data is obtained by reading this register and, thus, automatically clearing Bit 7.

Data to be transmitted is written to the TDR. This automatically clears Bit 7 of the Transmitter CSR. Here the data will remain until the transmitter is ready. The data is then placed into the transmitter setting Bit 7.

### ERROR REGISTERS

Each channel contains a 4 bit error register which is comprised of Bits 15 through 12 of the RDR.

Bit 12 is the Parity Error (PE) Bit. A "1" indicates the receiver parity does not match the parity selected by the format jumpers. The PE bit remains set until parity matches on a succeeding character. When parity is inhibited, this bit always reads zero.

Bit 13 is the Framing Error (FE) Bit. A "1" indicates the first stop bit was invalid. The FE bit will stay set until the next valid character's stop bit is received.

Bit 14 is the Overrun Error (OE) Bit. A "1" indicates that the last character was not read from the RDR before a new character was received. The OE is reset at the next character's stop if Bit 7 of the Receive CSR cleared.

Bit 15 is the Error Flag (EF) and is the logical "oring" of the PE, FE, and OE bits. The setting of any error bit will set this bit.

### EIA CIRCUIT

The EIA circuit for each channel consists of a differential line driver, line receiver, and a single ended line driver. Through the use of wire wrap jumpers, each channel can be configured to operate as RS-232C, RS-422, or RS-423.

Channels operating as RS-232C or RS-423 will configure the differential line receiver to operate single ended and utilize the single ended line driver. The slew rates of the line drivers are controlled by changing external resistors.

Channels which operate as RS-422 configure the differential line receiver for differential operation by adding a 100 ohm termination resistor, and utilize the differential line driver.

### BAUD RATE GENERATOR

The baud rate generator consists of a crystal oscillator and divider. The oscillator base frequency is 614.4 kHz which is divided to yield the nine baud rate clocks. Each channel can operate at any one baud rate independent of the other channels.

### MODES OF OPERATION

Each channel of the 304 can operate in various line disciplines, data formats, and baud rates. The base address can be set so that the board can reside in any I/O page location. The vector can also be set to any address from 0, to 7748, and the interrupt level can be set to 4, 5, 6, or 7. All of these operation modes are configured by setting wire wrap jumpers. Table 2 is a summary of the jumper selectable modes which the board can be configured to.

### TABLE 2

### Jumper Selectable Modes of Operation

| Mode Description     | Mode Selection                                                              |

|----------------------|-----------------------------------------------------------------------------|

| * Line Discipline    | RS-232C, RS-422, or RS-423                                                  |

| * Baud Rate          | 150, 300, 600, 1200, 2400, 4800, 9600, 19.2K, 38.4K, External               |

| * Serial Data Format | Data Bits, 7 or 8 Stop Bits, 1 or 2 Parity, Odd, Even, None                 |

| Base Address         | 160000 <sub>8</sub> to 177740 <sub>8</sub>                                  |

| Vector Base Address  | Ø to 740 <sub>8</sub>                                                       |

| Console              | Enable Channel 4 as System<br>Console<br>Address CH 4 = 177560 <sub>8</sub> |

|                      | Vector CH4 = 608                                                            |

| Halt/Reboot on Break | Channel 3                                                                   |

| Interrupt Level      | 4, 5, 6, or 7                                                               |

<sup>\*</sup> Channel to Channel Configurable

### FACTORY CONFIGURATION

The Model 304 is shipped configured as follows:

### TABLE 3

Base Address 1765008

Vector Base Address 3008

CH3 Console Enabled Yes

CH3 Halt on Break Enabled

\* Serial Data Format 1 Stop Bit, 8 Data Bits,

No Parity

\* Line Discipline RS232C \* Baud Rate 9600

Interrupt Level 4 (LSI-11)

\* All Channels

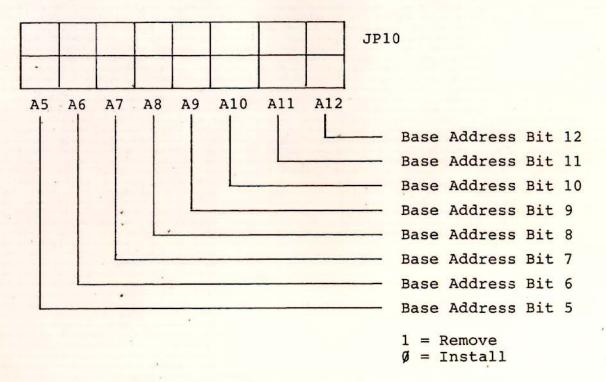

### SETTING THE BASE ADDRESS

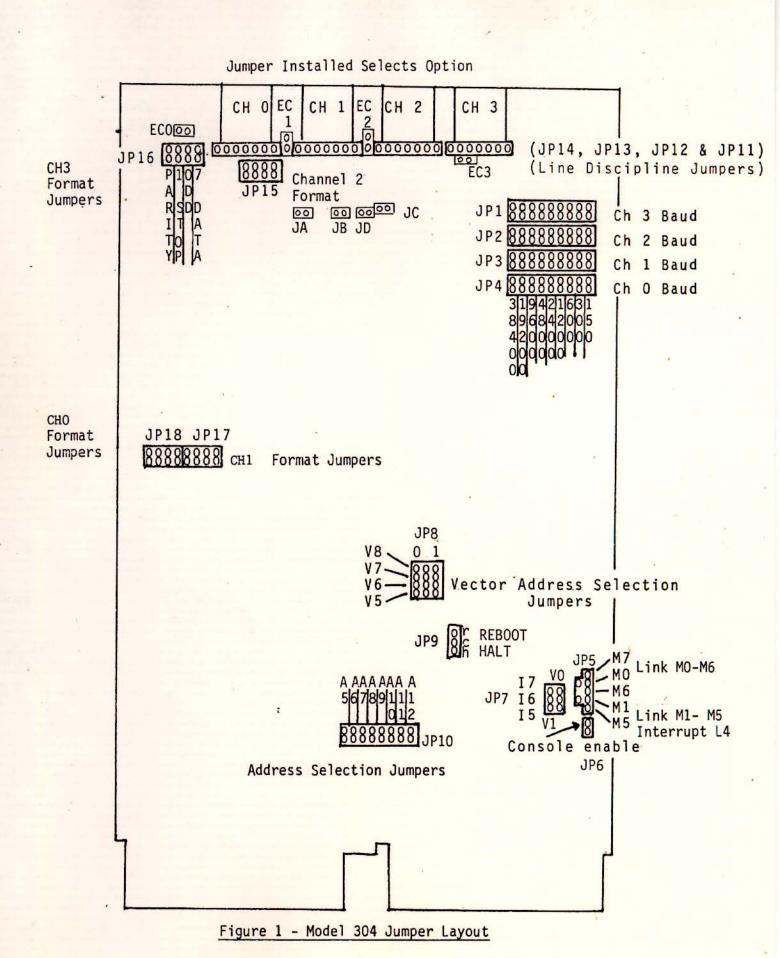

The 304's base address can be set to reside anywhere within the I/O page. the location of the base address jumper (JP10) is illustrated on Figure 1. To change the board's base address requires reconfiguring the base address jumpers.

Figure 2 illustrates the base address jumper post arrangement. The base address jumpers are arranged as eight pairs labeled A5 through A12. To set an address bit to a 1 requires no connection between the pair of jumper posts labeled for that bit. To set an address bit to a Ø requires installing a jumper between the pair of jumper posts for that bit.

As an example, the factory configured base address is 176500g. To set this base address requires installing jumpers at A5, A7, and A9 and removing any jumpers at A12, A11, A10, A8, and A6.

Figure 2 - Base Address Jumpers JP10

### SETTING THE VECTOR ADDRESS

The 304's vector address can be set from Ø to 7408. The location of the vector selection jumpers (JP8) is illustrated on Figure 1. The vector selection jumpers are comprised of four sets of jumper posts, three across. Each set is labeled according to the vector bit which it controls.

Setting a vector bit to a 1 requires installing a jumper between the right post and the center post. To set a bit to a Ø requires installing a jumper between the left and center post. Figure 3 illustrates the vector selection jumper.

As an example, the factor configured base vector address is 300<sub>8</sub>. To select this vector address requires installing jumpers between the left and center posts at V8 and V5 and the right and the center posts of V6 and V7.

| Vector | Address | Bit | 8 | - | V8 | 0 | 0 | 0 |     |

|--------|---------|-----|---|---|----|---|---|---|-----|

| Vector | Address | Bit | 7 | - | V7 | 0 | 0 | 0 | TDO |

| Vector | Address | Bit | 6 | _ | V6 | 0 | 0 | 0 | JP8 |

| Vector | Address | Bit | 5 | - | V5 | 0 | 0 | 0 |     |

Figure 3 - Vector Address Selection Jumpers JP8

TABLE 4

Interrupt Level Selection Jumpers

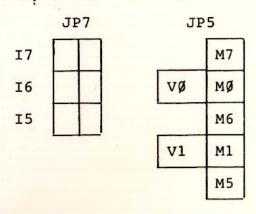

| Level |     | Jumper Post JP5* |    | Jump | Jumper Post JP7** |    |  |

|-------|-----|------------------|----|------|-------------------|----|--|

|       | 10. | M1               | мø | 15   | 16                | 17 |  |

| 4     |     | М5               | M6 | R    | R                 | R  |  |

| 5     |     | V1               | М6 | I    | ,R                | R  |  |

| 6     |     | V1               | м7 | R    | I                 | R  |  |

| 7     |     | V1               | VØ | R    | I                 | I  |  |

\*Note: Install jumpers from jumper posts M1 and MØ to the jumper posts listed in each column according to the interrupt level desired. No other jumpers should be installed

\*\*Note: R = Remove I = Install

### SETTING THE INTERRUPT LEVEL

Setting the 304's interrupt level is done by configuring jumper posts JP5 and JP7 according to Table 4. Figure 1 illustrates the location of these jumper posts and Figure 4 illustrates these jumper posts in greater detail.

Figure 4 - Interrupt Level Selection Jumpers JP5 and JP7

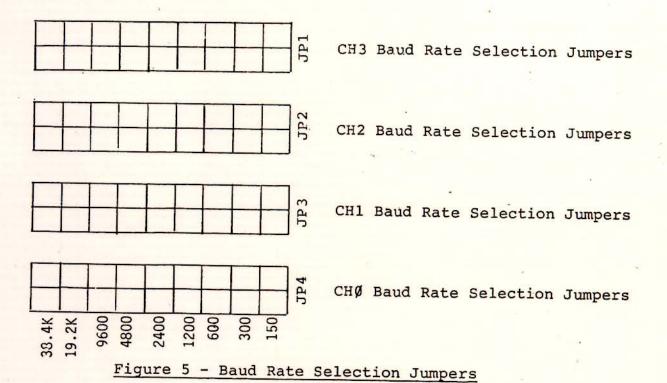

### SETTING THE BAUD RATE

Each channel can be set to operate at one of nine jumper selectable baud rates from 150 to 38.4K baud. Figure 5 illustrates the baud rate selection jumpers and Figure 1 illustrates their location on the 304.

In addition to the on-board baud rates, the user can use an external clock. The external clock is input through pin 1 of a channels I/O connector. The baud rate jumpers must also be completely removed from that channels baud rate jumper block and external clock jumper for that channel must be installed. These may be located by refering to Figure 1. Channel 0 through 3's external clock jumpers correspond to jumper post ECØ through EC3, respectively.

The baud rate jumpers are divided into four groups of nine pairs. Each group is used to select a baud rate for each channel, and each jumper pair for each baud rate. To set the baud rate requires installing a jumper at the appropriate jumper pair within the baud rate selection jumpers for the channel.

### ENABLING THE CONSOLE

Channel 3 can be enabled as the system console independent of the base and vector address settings. To enable this option requires installing jumper JP6. To disable this option requires removing jumper JP6. Refer to Figure 1.

When the console is enabled, Channel 3 will respond to addresses 177560<sub>8</sub> to 177566 and will output a vector of 60 and 64 for the receiver and transmitter interrupts, respectively. Caution should be employed when the console is enabled so as not to set the base address equal to 177540 or a confilit will exist between Channel 2 and Channel 3. When the console is disabled, all jumpers must be removed from JP9 (refer to Figure 1).

### SYSTEM HALT OR REBOOT

Any device communicating through Channel 3 can generate a system halt or power up initialization by outputing a "BREAK."

To generate a system halt on break requires installing a jumper at JP9 (Figure 1) from C to H. To generate a power fail reset, connect C to R. Refer to Figure 1 for jumper block JP9's location. Removing either jumper disables these functions completely.

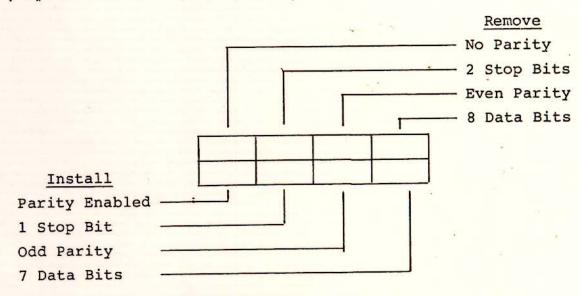

### SETTING THE SERIAL DATA FORMAT

Each channel of the 304 can be configured to operate in the following data formats:

7 or 8 Data Bits 1 or 2 Stop Bits Odd, Even, or with No Parity

Jumper posts JP18, JP17, JP15, and JP16 (Figure 1) are used to set the serial data format of Channels Ø through 3, respectively. The jumper configurations of the various options are illustrated in Figure 6. As an example, the 304 is shipped configured for eight data bits, one stop bit, and no parity. This requires installing the one stop bit imper and removing all the rest.

Figure 6 - Serial Data Format Jumper Block Detail

JP15 (CH 2), JP16 (CH 3), JP17 (CH1) and JP18 (CHØ)

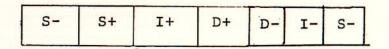

### SETTING THE LINE DISCIPLINE

Each channel of the 304 can operate in any one of the following EIA line disciplines:

RS-232C RS-422 RS-423

The jumper blocks used to configure Channels # through JP14, JP13, JP12, and JP11 (Figure 1), respectively. Table 9 illustrates the jumper configuration to set up each channel. As an example, the 304 is shipped from the factory with each channel set up to operate in RS-232C. This requires jumpering S+ to I+ and S- to I-. Figure 6 illustrates the layout of the line discipline jumper blocks.

### TABLE 9 Line Discipline Jumper Configuration

|   | Line<br><u>Discipline</u> | Jumper<br>Configuration |    |

|---|---------------------------|-------------------------|----|

|   | RS-232C                   | I+ to S+, I- to         | s- |

| * | RS-422                    | I+ to D+, I- to         | D- |

|   | RS-423                    | I+ to S+, I- to         | S- |

<sup>\*</sup> Add 100 ohm termination resistor, (RA, RB, RC, RD)

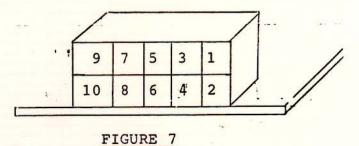

### FIGURE 7

### Line Discipline Jumper Block Layout

JP14, JP13, JP12, JP11

When a channel is set up to operate in RS-422, a 100 ohm termination resistor must be installed at the input of the differential receiver. This is accomplished by installing jumpers JA through JD according to Table 10.

TABLE 10

### RS-422 Resistor Installation Jumper Guide

| Channel | Ø | Install | Jumper | JA |

|---------|---|---------|--------|----|

| Channel | 1 | Install | Jumper | JB |

| Channel | 2 | Install | Jumper | JС |

| Channel | 3 | Install | Jumper | JD |

During data communication over long data leads, it may be necessary to change the rise and fall times of the single ended line drivers used in RS-423 to reduce line reflections and the potential of data errors. R13 controls the transition time for Channels Ø and 1 and R14 controls Channels 2 and 3. The resistor installed at the factory is a 22K which sets the transition time at 2.2µs. Table 11 is a list of recommended resistor values as a function of baud rate which should be installed if line reflections become a problem.

RS-423 Slew Rate Resistor Values

| Baud Rate | Resistor<br>Value in Ohms | Nominal<br>Transition Times |

|-----------|---------------------------|-----------------------------|

| 150       | 1 Megohm                  | 100 µsec                    |

| 300       | 1 Megohm                  | 100 µsec                    |

| 600       | 1 Megohm                  | 100 µsec                    |

| 1200      | 820K Ohm                  | 82 µsec                     |

| 2400      | 430K Ohm                  | 43 µsec                     |

| 4800      | 200K Ohm                  | 20 µsec                     |

| 9600      | 100K Ohm                  | 10 µsec                     |

| 19.2K     | 51K Ohm                   | 5.1 µsec                    |

| 38.4K     | 22K Ohm                   | 2.2 µsec                    |

### READER RUN PULSE

The reader run pulse is used to control a paper tape reader. To use this control requires connecting P to I- at the appropriate line discipline jumper block (Figure 1). Figure 6 illustrates the location of this jumper with the line discipline jumper block.

### SERIAL INTERFACE

Figure 1 illustrates the connector location for each channel.

### -CONNECTOR DESCRIPTION

Each channel is interfaced through a 10 pin header. Figure 7 illustrates the pin-out location. The mating connector is manufactured by AMP, Inc. Table 12 lists the parts which are required to assemble the mating connector. The connector may be obtained through AMP, AMP distributors, or GTSC.

TABLE 12

Model 304 Connector Assembly Parts List

| AMP P/N | Description     | Quantity/Connector |     |

|---------|-----------------|--------------------|-----|

| 87133-5 | Connector Shell | 1                  | (*) |

| 87179-1 | Key Pin         | 1                  |     |

| 87165-2 | Pins            | 9 •                |     |

|         |                 |                    |     |

Model 304 Header Pin-out

The pin-out description of each header is as follows:

| Pin No.    | Description       |

|------------|-------------------|

| N-1        | Clock I/O         |

| 2 :        | Signal Ground     |

| 3          | Transmit Data + V |

| N 4        | Transmit Data -   |

| 5          | Signal Ground ~   |

| N-6        | Key (No Pin)      |

| <b>—</b> 7 | Receive Data -    |

| 8          | Receive Data +    |

| و          | Signal Ground     |

| N-10       | +12 Volts (Fused) |

When a channel is configured for RS-232C or RS-423, Pin 7 must be externally tied to signal ground. This is typically done by connecting Pin 7 to Pin 9. Pin 1 is the external clock input.

### LINE DISCIPLINE, CABLE LENGTH & DATA RATES

The two basic methods for electronic communications are single ended transmission and differential transmission. RS-232 was developed for single ended transmission over short distances at slow data rates. RS-423 extends the maximum data rate and cable length beyond that of RS-232. It also provides for wave shaping dependent on data rate and wire length to control reflections.

For communications over long distances, differential transmissions (RS-422) should be used to nullify effects of ground shifts and noise signals which appear as common mode. Table 13 lists the maximum recommended cable length and data rates for each line discipline.

### TABLE 13

### Key Aspects of RS-232,

### RS-423 & RS-422

| Specification                                  | RS-232C                | RS-423                   | RS-422       |

|------------------------------------------------|------------------------|--------------------------|--------------|

| Mode of Operation                              | Single-<br>ended       | Single-<br>ended         | Differential |

| No. of Drivers & Receivers allowed on one line | 1 Driver<br>1 Receiver | 1 Driver<br>10 Receivers |              |

| Maximum Cable Length                           | 50 feet                | 4000 feet                | 4000 feet    |

| Maximum Data Rate                              | 20 kb/s                | 100 kb/s                 | 10 mb/s      |

### PROGRAMMING

Figure 8 illustrates the functions of the four 16 bit registers which comprise each channel. Thus, the Model 304 occupies 16 contiguous blocks in the I/O page \*. The registers which make up each channel are:

Receiver Control Status Register (RCSR)

Receiver Data Register (RDR)

Transmitter Control Status Register (TCSR)

Transmitter Data Register (TDR)

Table 14 illustrates the relationship between each channel's registers and the base address. When the console is enabled, any attempt to address Channel 3 through an address other than the console address will cause a bus time out error.

Testing Bit 7 of the RCSR is used to indicate that the UART has received new data. Reading the RDR will clear Bit 7. Setting Bit 6 of the RCSR will enable the receiver interrupts. When Bit 7 is set, an interrupt will be generated.

Bit Ø of the RCSR is used to generate the reader run pulse by setting this write only bit. This action will also clear Bit 7 of the RCSR.

Bits Ø through 7 of the RDR contain the data received by the UART. Bits 12 through 15 indicate any errors which have occurred during the reception of data.

Bit 7 of the TCSR indicates the status of the transmitter. When this bit is set, the transmitter is ready to receive a new byte of data for transmission. When this bit is cleared (Bit  $7 = \emptyset$ ), the transmitter is busy and no attempt to write the data to the TDR should be made. Setting Bit 6 of the TCSR will allow interrupts to be generated when Bit 7 is set.

Bit Ø of the TCSR is a read/write bit used to transmit a continuous break. A "1" written to Bit Ø will transmit a break (continuous Ø), a zero clears the break transmission.

<sup>\*</sup> This only holds true if Channel 3 is not configured as the console.

Data which is to be transmitted is written to the TDR, but only if Bit 7 of the TCSR is set.

Table 15 lists the relationship between the vector jumper settings and each channel. Note, Channel 3's vector is that of the console when the console is enabled.

Table 16 illustrates the register and vector address when Channel 3 is configured as the system console.

TABLE 14

### Register Address Offset

| Register Description                                                                                                  | Base Address Offset (Octal)                                         |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Channel Ø Receiver CSR Channel Ø Receiver Data Register Channel Ø Transmitter CSR Channel Ø Transmitter Data Register | Base Address +0 Base Address +2 Base Address +4 Base Address +6     |

| Channel 1 Receiver CSR Channel 1 Receiver Data Register Channel 1 Transmitter CSR Channel 1 Transmitter Data Register | Base Address +10 Base Address +12 Base Address +14 Base Address +16 |

| Channel 2 Receiver CSR Channel 2 Receiver Data Register Channel 2 Transmitter CSR Channel 2 Transmitter Data Register | Base Address +20 Base Address +22 Base Address +24 Base Address +26 |

| Channel 3 Receiver CSR Channel 3 Receiver Data Register Channel 3 Transmitter CSR Channel 3 Transmitter Data Register | Base Address +30 Base Address +32 Base Address +34 Base Address +36 |

### TABLE 15

### Vector Address Offset

| Interrupt<br>Description |           |                 | Vector Base<br>Address Offs | et |

|--------------------------|-----------|-----------------|-----------------------------|----|

| Channel Ø                |           |                 | ø<br>4                      | 10 |

| Channel 1<br>Channel 1   |           |                 | 10<br>14                    |    |

| Channel 2<br>Channel 2   |           | Eq.             | 20<br>24                    |    |

| Channel 3<br>Channel 3   | ;4<br>;4; | ca <sub>2</sub> | 30<br>34                    |    |

### TABLE 16

### Console Register & Vector Addresses

### When Console Option is Enabled

| Channel 3 Register Description       | Register Address |

|--------------------------------------|------------------|

| Receiver CSR                         | 1775608          |

| Receiver Data Register               | 1775628          |

| Transmitter CSR                      | 1775648          |

| Transmitter Data Register            | 1775668          |

| Receiver Interrupt Vector Address    | 608              |

| Transmitter Interrupt Vector Address | 648              |

### RECEIVER CSR

## RECEIVER DATA REGISTER

## TRANSMITTER CSR

# TRANSMIT DATA REGISTER

| Ø TD;   | ø       | 0 | 0     | 0       | 0 0     |

|---------|---------|---|-------|---------|---------|

| Q   TD7 | CO. Co. | 9 | 0 0 0 | 0 0 0 0 | 0 0 0 0 |

FIGURE 8 (Cont.)

Model 304 Serial I/O Port Register Formats